What changes in DDR4 vs DDR5 DIMMs?

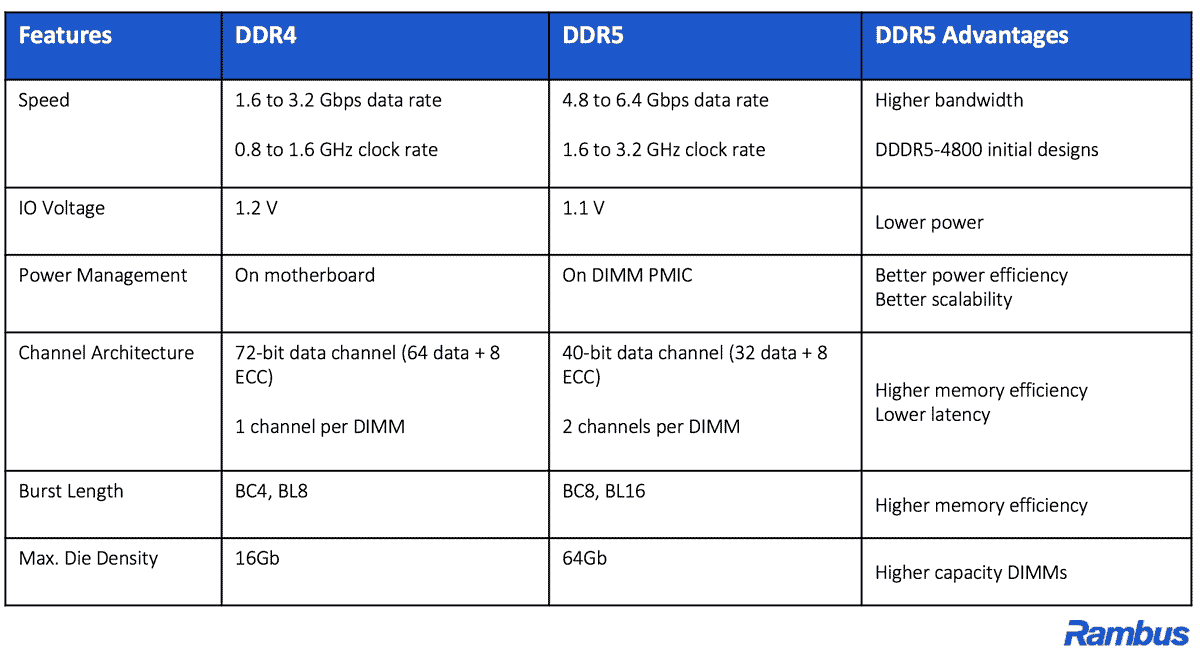

The top six most significant specification advances made in the transition from DDR4 to DDR5 DIMMs are shown in Table 1 below.

DDR5 scales to 6.4 Gbps

You can never have enough memory bandwidth, and DDR5 helps feed that insatiable need for speed. While DDR4 DIMMs top out at 3.2 gigabits per second (Gbps) at a clock rate of 1.6 gigahertz (GHz), initial DDR5 will deliver a 50% bandwidth increase to 4.8 Gbps.

DDR5 memory will ultimately double the data rate of DDR4 DRAM reaching 6.4 Gbps. New features, such as Decision Feedback Equalization (DFE), were incorporated in DDR5 enabling the higher IO speeds.

Lower voltage means lower power

A second major change is a reduction in operating voltage (VDD), and that will translate to lower power. With DDR5, the DRAM and buffer chip registering clock driver (RCD) voltage drops from 1.2 V down to 1.1 V. However, lower VDD means smaller margin for noise immunity which designers will have to be cognizant of for their implementations.

New power architecture for DDR5

A third change, and a major one, is power architecture. With DDR5 DIMMs, power management moves from the motherboard to the DIMM itself. DDR5 DIMMs will have a 12-V power management IC (PMIC) on DIMM allowing for better granularity of system power loading.

The PMIC distributes the 1.1 V VDD supply, helping with signal integrity and noise with better on-DIMM control of the power supply.

DDR5 vs DDR4 channel architecture

Another major change with DDR5, number four on our list, is a new DIMM channel architecture. DDR4 DIMMs have a 72-bit bus, comprised of 64 data bits plus eight ECC bits. With DDR5, each DIMM will have two channels. Each of these channels will be 40-bits wide: 32 data bits with eight ECC bits. While the data width is the same (64-bits total) having two smaller independent channels improves memory access efficiency. So not only do you get the benefit of the speed bump with DDR5, the benefit of that higher MT/s is amplified by greater efficiency.

In the DDR5 DIMM architecture, the left and right side of the DIMM, each served by an independent 40-bit wide channel, share the RCD. In DDR4, the RCD provides two output clocks per side. In DDR5, the RCD provides four output clocks per side.

The 32-bit data of each 40-bit channel consist of four 8-bit lanes, and each of these lanes gets an independent clock signal from the RCD. Giving each lane an independent clock improves signal integrity, helping to address the lower noise margin issue raised by lowering the VDD (from change #2 above).

Longer burst length

The fifth major change is burst length. DDR4 burst chop length is four and burst length is eight. For DDR5, burst chop and burst length will be extended to eight and sixteen to increase burst payload. Burst length of sixteen (BL16), allows a single burst to access 64 Bytes of data, which is the typical CPU cache line size. It can do this using only one of the two independent channels. This provides a significant improvement in concurrency and with two channels, greater memory efficiency.

DDR5 supports higher capacity DRAM

A sixth and final change to highlight for DDR5 is support for higher-capacity DRAM devices. With DDR5 buffer chip DIMMs, the server or system designer can use densities of up to 64 Gb DRAMs in a single-die package. DDR4 maxes out at 16 Gb DRAM in a single-die package.

DDR5 supports features like on-die ECC, error transparency mode, post-package repair, and read and write CRC modes to support higher-capacity DRAMs.