Two breakthroughs for spintronic logic devices

At the 2018 IEEE International Electron Devices Meeting (IEDM), imec, and its partners presented an experimental demonstration of full majority gate operation based on spin-wave interference in scaled devices. Circuit-level benchmarking recommends majority gates based on spin-waves for ultralow power applications.

Imec also demonstrated the first logic gate implementation based on magnetic domain wall propagation. Fully integrated logic devices were fabricated on 300mm wafers using CMOS compatible processes. These breakthroughs constitute the foundation of a robust spintronics platform that will be used for functional spintronic logic components for low-power applications

In the quest for low-power electronics, imec is reportedly investigating majority gates based on spintronics phenomena as a possible path towards more efficient circuits. Majority gates are ‘democratic’ devices that return true if more than 50% of their inputs are true. Complex logic operation such as addition and multiplication can be emulated in a much more compact and energy efficient way than with the conventional NAND-based circuits. Imec has reported breakthroughs for two different implementations of majority gates. Both implementations are based on spintronics, which exploits the magnetisation state in a ferromagnet rather than the charge of electrons to perform logic operations.

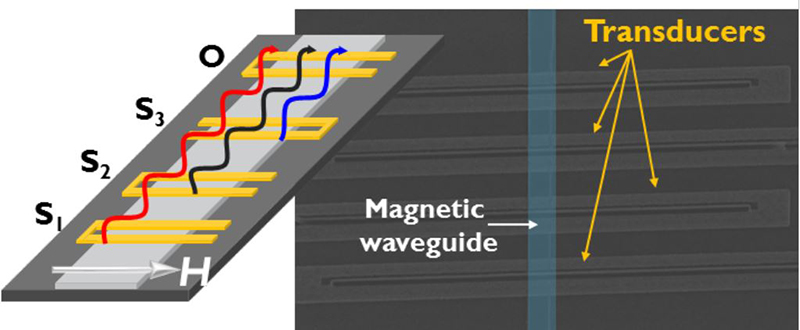

A first is reported for devices that use the interference of spin waves to enable logic operation. While basic functionality was shown earlier for large-scale devices, imec, in collaboration with University Paris-Sud, has experimentally demonstrated full majority gate operation in sub-µm devices. The research team has verified the full truth table of a majority logic function, which lists all possible configurations of the input variables together with the result of the operation of those values. They also demonstrated the ability to distinguish between strong and weak majority, making these devices attractive for neuromorphic applications.

The second breakthrough is reported for devices based on magnetic domain wall generation and propagation, another spintronics phenomenon. Imec, in collaboration with Intel and University Paris-Sud reports first logic function demonstration based on domain wall propagation. For the first time, it was demonstrated the nucleation, propagation, and detection of magnetic domain walls with magnetic tunnel junctions connected by a free layer ferromagnet.

The second breakthrough is reported for devices based on magnetic domain wall generation and propagation, another spintronics phenomenon. Imec, in collaboration with Intel and University Paris-Sud reports first logic function demonstration based on domain wall propagation. For the first time, it was demonstrated the nucleation, propagation, and detection of magnetic domain walls with magnetic tunnel junctions connected by a free layer ferromagnet.

The domain walls are generated via spin transfer torque. The motion of the domain walls was monitored and verified via tunnel magnetoresistance measurements through a series of adjacent magnetic tunnel junctions which share the free layer. The devices were fabricated on 300mm wafers using CMOS compatible production processes. Imec’s capability to pattern these delicate structures is a key enabler for the fabrication process.

Imec’s research into advanced logic scaling is performed in cooperation with imec’s key CMOS program partners including GlobalFoundries, Huawei, Intel, Micron, Qualcomm, Samsung, SK Hynix, Sony Semiconductor Solutions, TOSHIBA Memory, TSMC and Western Digital.