To integrate or not to integrate

Dr Mike Coulson, SWINDON Silicon Systems, weighs up the pros and cons of integrating ADCs in ASICs.

An Application Specific Integrated Circuit (ASIC) is a custom designed silicon chip, which replaces numerous discrete components on a PCB to improve performance whilst reducing cost, physical size and power consumption. ASICs are often used in sensor systems, where continuously varying voltages or currents are digitised by an Analogue to Digital Converter (ADC) before being digitally processed. When the ADC is absorbed into the ASIC, both analogue and digital discrete components may be replaced and the benefits of using an ASIC become particularly notable.

The benefits of integration

When there is the capability to add ADCs to an ASIC, there is the facility to absorb both the analogue and digital aspects of the design into a single package. This is preferable to using a discrete ADC for several reasons. Firstly, the separate package of the ADC is eliminated and so the system becomes smaller and more mechanically robust.

Secondly, the cost of the separate ADC is eliminated. Chip design overheads will increase, but not dramatically, providing the supplier has a good breadth of experience and a portfolio of past designs to draw elements from.

Thirdly, uniting both analogue and digital functions on a single chip brings scope for the entire signal path to come under the responsibility of the ASIC supplier. This means that a complete system, from pre-amplifiers to digital signal processing, can be simulated together and remains the responsibility of one company. The ASIC test process will then guarantee operation of a cohesive system, rather than validating a smaller building block. Costs will be reduced here too, given that only one package need be handled by the test facility.

Finally, a discrete ADC must be chosen from a limited set of available devices, so parts may be over specified in some regards just to achieve the necessary performance in others. This will contribute to cost and power consumption. In contrast, an ASIC designer has control over every aspect of an integrated converter and can optimise it for the task in hand.

Types of ADCs and their application

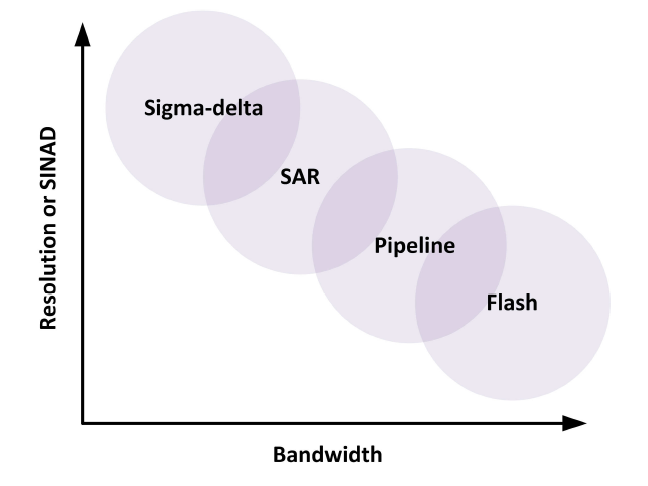

The first and most important design decision is the type of ADC to use. There are numerous techniques for performing analogue to digital conversion. Some excel at delivering high speed results, yet are not suited to high resolutions. Others are restricted to low bandwidths, yet can offer high precision. Four of the key circuit architectures are Flash, Pipeline, Successive Approximation Register (SAR) and Sigma-delta. It is common to see them spanning a plot of bandwidth versus resolution, as shown in Fig 1 (above).

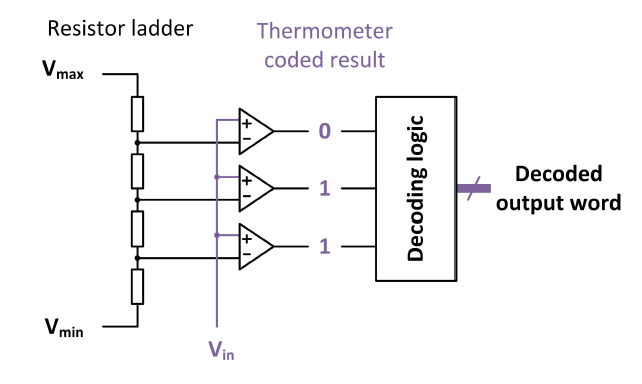

In an N-bit flash ADC, a set of 2N-1 comparators is fed with staggered reference voltages that span the input range, as shown in Fig 2 (above). This architecture is extremely fast because the conversion is completed in a single action. However, even an 8-bit ADC requires 255 comparators, so flash converters are both large and power hungry. They should therefore, be reserved for use when bandwidth is an absolute priority.

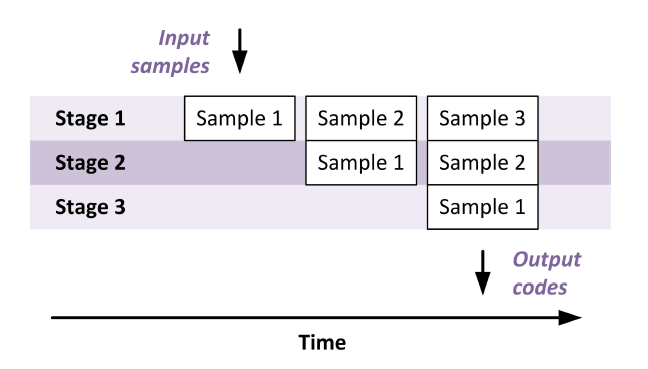

Pipeline ADCs achieve higher resolutions than flash converters, but maintain respectable bandwidths by performing each conversion in multiple stages. Like a production line, each stage of the conversion is handled by a different part of the circuit. At any point in time there are multiple conversions underway and each is at a different stage of completion - the principle is shown in Fig 3 (below).

However, as any given sample must be processed by every stage in turn, an appreciable ‘pipeline delay’ is accumulated. This delay may be unacceptable, especially in closed-loop control applications where it may cause instability. Furthermore, as numerous stages operate simultaneously, pipelined ADCs tend to consume appreciable power and area.

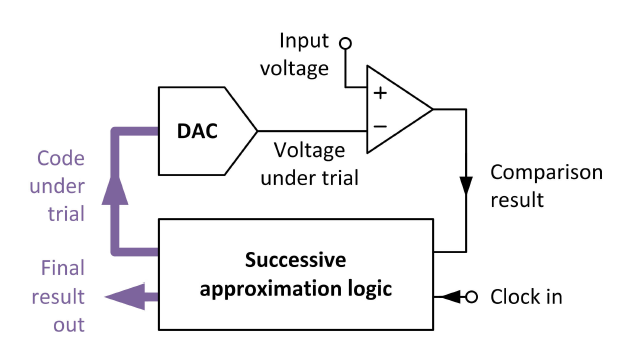

For mid-bandwidth applications where resolutions of 10-14-bits are required, successive approximation ADCs are often best suited. In a SAR ADC, the output code is arrived at through a series of iterations, which can be understood by examining Fig. 4 (below).

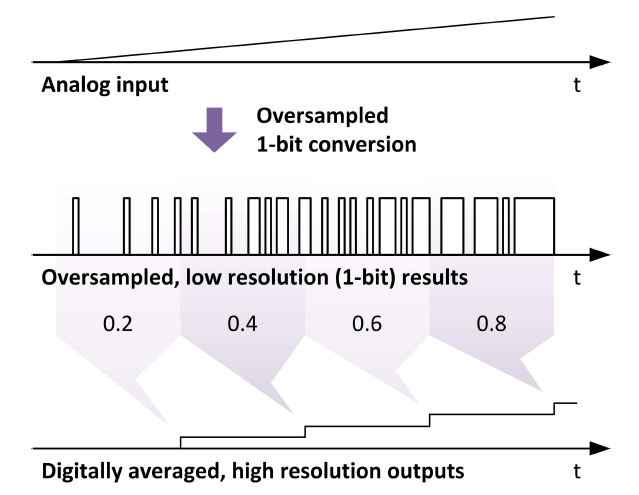

When the highest resolutions are required and low bandwidths are tolerable, sigma-delta ADCs are considered. These employ a technique called oversampling whereby many noisy, low resolution conversions are digitally averaged to produce a single high precision result. The low resolution is commonly only 1-bit, so the oversampled result amounts to the digital pulse train of Fig. 5 (above). The oversampling ratio dictates how many low resolution conversions correspond to a single high resolution output - ratios of 1,000 are typical, explaining the restricted bandwidths that can be achieved.

The sigma-delta architecture is a particular type of oversampling ADC, which employs specific mathematical processes to calculate the low resolution results. However, as the underlying mathematics is non-linear, stability is difficult to guarantee, and the design will often involve extensive abstract modelling. Both skill and experience are required on the part of the ASIC supplier in order to guarantee success.

The challenges of integration

Performing on-chip data conversion is not trivial and care must always be taken when moving sensitive analogue circuits into the same package as noisy digital logic. It is essential for an ASIC designer to spot potential interference mechanisms within a chip and to assess each circuit’s susceptibility through simulation. Fully differential circuit architectures are particularly robust and should be adopted wherever possible.

To integrate or not

In applications that demand cutting edge performance from an ADC, integration is probably not the correct route to follow. High performance converters require specially chosen fabrication processes and benefit from being isolated in their own packages.

However, in the vast majority of automotive and industrial applications an integrated ADC proves cheaper, smaller and more convenient than using a separate chip. Whilst some additional silicon area and ASIC design effort are required, these costs should not significantly impact the net benefits. Remember, once the ADC is integrated, there is scope for additional elements of the analogue signal chain to be absorbed too. In this way, the potential gains multiply - one ASIC supplier takes responsibility for the whole signal path, and the production test process qualifies all elements therein.