GaN - promise to reality

The next generation of power electronics is taking shape, argues Markus Behet, EpiGaN. The wide-bandgap compound semiconductor material is suited for switching devices that operate at high frequencies without suffering major losses.

GaN’s drastically lower on-state resistance combined with considerably reduced in/output capacitances mean higher switching frequencies leading to a substantial volume reduction of passive components such as inductors, transformers and capacitors. Manufacturers of GaN-on-Si wafers are striving to make GaN wafer processing compatible with the tools and procedures in existing Si-CMOS fabs.

Applications of GaN transistors, including battery chargers, motor drives, solar inverters and consumer-oriented power supplies all point to significant performance improvements. The recent acquisition of GaN pioneer, International Rectifier, by power semiconductor maker, Infineon, together with its co-operation with Panasonic, is the latest indication of GaN markets starting to take off and complement currently existing SiC power devices.

Market outlook

The promising outlook for commercial GaN products allows epi-wafer suppliers to think about standardisation procedures for wafers to improve product stability in high-volume manufacturing processes. EpiGaN offers wafer structures with defined targets in terms of their electrical characteristics, especially in the latest generation of wafers up to 200mm in diameter for 650V power switching devices. Manufacturing these wafers is not easy since stack structures have to be carefully controlled to meet the higher voltage requirements, as well as strict bow specifications required by Si-CMOS manufacturing lines.

Figure 1: EpiGaN’s epi-wafer

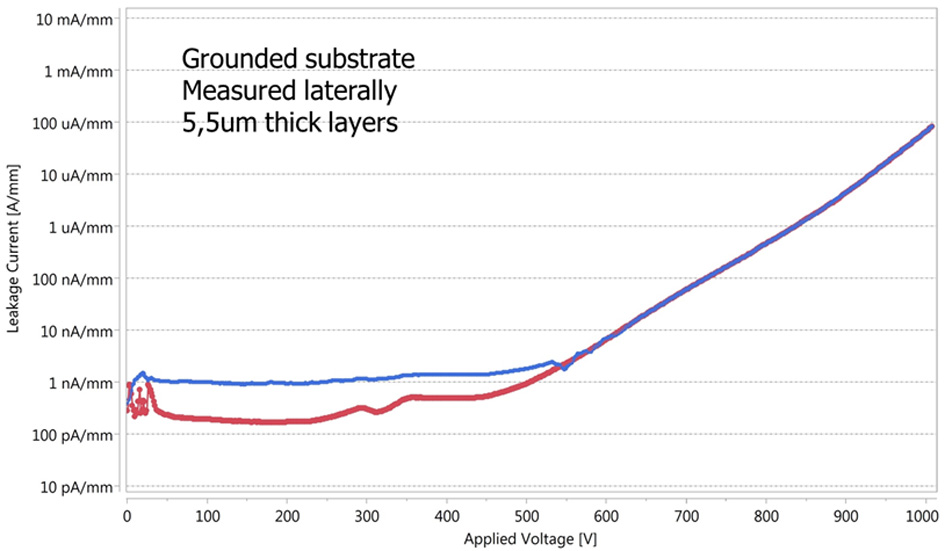

EpiGaN now manufactures GaN-on-silicon wafers with a breakdown voltage above 800V and a very small leakage current at the rated voltage of 650V. Yet this is by no means the upper limit. Recent research work has yielded FETs with a breakdown above 2kV. Today’s breakdown voltage limitations are confining GaN transistors to power electronics products in the 30 to 600V range.

On the road to 1.2 and 2kV

Devices with 600V breakdown voltage have been released recently by Infineon, Panasonic, Transphorm and GaN Systems. It won't be long before devices operating at 1,200V can be added to the list. This will enable the replacement of two silicon MOSFETs with a single GaN HEMT, to substantially trim the cost and weight of power converters that operate at much higher switching frequencies compared to incumbent Si-based solutions.

Wide-band-gap semiconductor AlGaN/GaN heterostructures have a bandgap value of 3.4 to 6.2eV, depending on the material composition. This enables GaN devices to work at higher temperatures, due to low intrinsic carrier concentrations. Field strength an order of magnitude higher than that of silicon, and high carrier mobility and concentration associated with the two-dimensional electron gas (2DEG) formation at the interface of an AlGaN/GaN heterostructure in switching applications, offer a low on-resistance combined with high-frequency switching.

Affordability

GaN-on-Silicon currently is the most cost-efficient, wide-bandgap technology, and is set to benefit from the economies of scale of Si technology. It is feasible to deposit advanced heterostructures on silicon wafers up to 200mm in diameter. There is also an ongoing effort to develop process compatibility with standard Si-CMOS technology. Further cost reductions could be realized by using existing lines at 200mm silicon fabs.

A recent study by French market researcher, Yole Development, foresees the annual market volume for GaN devices approaching $600m in 2020. This is a compound growth rate of 120% from today’s $25m.

Of foremost concern for growing GaN-on-Si is the mechanical stress occurring in GaN-on-Si wafers due to the severe crystalline and temperature mismatch between GaN and Si. Untreated this would lead to intolerable wafer warping and cracking.

In-situ SiN passivation

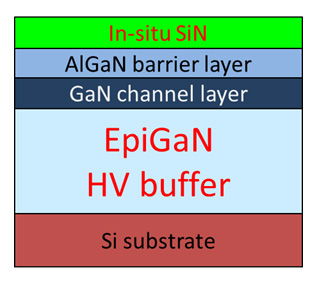

EpiGaN applies a specific sealing on top of GaN-on-Si wafers in the form of a Silicon-Nitride (SiN) passivation layer, which is about 50 to 100nm thick. As a consequence, there can be no exposure of GaN to the fab environment because there is silicon at the bottom and the top.

Figure 2: The layer structure ensures silicon top and bottom

The process was derived from the MOCVD growth of SiN using surface electrical passivation for III-Nitrides. The company applies this to a gate dielectric with a smooth and contamination-free surface to facilitate the technology use in Si-CMOS fabs.

In-situ deposited SiN films can also establish a substantially lower channel resistance (Ron) to meet a particular device specification. GaN FETs are laterally structured devices, so any performance optimisation requires a trimming of conduction losses. For switching applications, aluminum-rich barriers are preferred in an AlGaN/GaN structure, because this yields a higher piezoelectric field, higher current density and it lowers the on-resistance.

SiN cap advantages

The SiN capping layer also controls the filling of the surface states during device operation. It is believed that SiN can provide enough charge to neutralise the surface charge of the AlGaN barrier layer in a GaN-on-Si device so that its surface potential no longer contributes to 2DEG depletion. The SiN layer also adds device stability at elevated temperatures.

Another benefit is that it enables a higher aluminum concentration without significant material degradation. This is not the case in transistor structures with an uncapped or GaN-capped AlGaN/GaN 2DEG, where relaxation of the strained top AlGaN layer prevents high aluminum content in the top layer.

In combination with the SiN process, it is possible to replace the AlGaN layer with a pure AlN layer with a thickness of just 5nm. For a SiN/AlN/GaN design, sheet resistance falls to 235Ω/sq. Hall measurements indicate that the electron sheet concentration is 2.15 x 1013cm2 and electron mobility is 1,250cm2/Vs. These transport properties lead to devices with higher current densities and hence a more compact device design at lower cost. In addition the SiN/AiN/GaN structure enables the fabrication of transistor devices with high transconductance, even with a relatively large gate length.

Favourable electrical properties

Regarding economies of scale, GaN-on-Si devices offer inherently better electrical properties than Si, specifically a much lower on-resistance in relation to the active area. Additionally, the conduction and switching losses are significantly lower for GaN compared to Si FETs. In other words, much more power can be extracted more efficiently from a device of the same active area. There is four or five times more current to be obtained in a GaN device than in a Si device of the same size. Conversely, GaN devices can be made much smaller.

Figure 3: The latest generation can accommodate low leakage up to 650V

GaN can withstand much higher operating temperatures than Si junctions i.e. 250°C versus 125°C, but heat dissipation from a much smaller active area becomes a problem. With higher power loads on smaller devices, specific cooling measures must be taken. Packaging technology has to catch up with the new devices.

System lay-out considerations

Higher switching frequencies will force power system designers to re-design the magnetics components involved, especially in PFC (power factor correction) applications. Switch-mode power supplies with PFC for consumer laptops using GaN devices arethree to five times smaller in size, six times lighter in weight and they typically operate up to a few hundred MHz. This implies that system designers have to consider different passive component and packaging materials. Shielding and cooling structures will also have to be re-optimised for GaN.

EpiGaN, founded in 2010 as a spin-off from Belgian research center Imec, currently offers GaN epitaxial layers deposited crack-free on Si-wafers up to 200mm diameter or, for specific applications, on SiC. Its capabilities include in-situ SiN capping layer for surface passivation; wafer diameters up to 200mm processed involving SiN/AlGaN/GaN, SiN/AlN/GaN and (In)(Al)GaN-based heterostructures. Substrates offered are Si (111) and SiC.

The company delivers GaN-on-silicon wafers with a breakdown voltage above 800V with very low leakage current. Recent work has yielded FETs with a breakdown above 2kV. Future products based on this process will complement the existing range of four inch and 150mm epi-wafers for high-voltage and/or high-frequency applications. Processes for 200mm GaN epi-wafers operating at 600 and 1,200V are also being developed. Larger wafer sizes will spur a cost reduction and enable GaN to deliver in a field where, until now, no compound semiconductor has seriously challenged traditional silicon devices.