Alliance Memory launches LPSRAMs with embedded error-correction code

Alliance Memory announces that the company has expanded its portfolio of low power asynchronous SRAM (LPSRAM) products with new 1 and 4Mb devices that feature embedded error-correction code (ECC).

Compared to previous generation devices, the AS6CE1016A (1Mb) and AS6CE4016B (4Mb) offer better failure in time (FIT) and mean time to failure (MTTF) characteristics with reduced soft error rates (SER) for more reliable operation in a wide range of consumer, industrial, communications, and medical applications.

The LPSRAMs' ECC feature provides 1-bit error correction per byte, which makes them particularly suitable for low power applications and battery backup non-volatile memory applications. Data retention voltage for both devices is 1.5V with typical data retention current of 1µA for the 1Mb AS6CE1016A and 2µA for the 4Mb AS6CE4016B. The devices operate from a single power supply of 2.7 to 3.6V, and all inputs and outputs are fully TTL compatible.

With their enhanced performance, the new LPSRAMs are designed to meet the demands of a very wide range of applications, such as routers and switches in communications systems; programmable logic controllers in industrial automation systems; printers, gaming machines, musical instruments, and calculators; vending machines and ATMs; and elevator systems, control panels, and fire control systems.

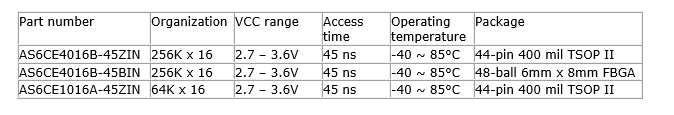

Key device specifications and package options are shown in the table below.

Device Specification Table:

Samples and production quantities of the AS6CE1016A (1Mb) and AS6CE4016B (4Mb) are in stock and available now.