A new take to identify conducted noise

A practical method to separate common mode and differential mode noise enables power supply designers to reduce design time and BoM

EMI from switching regulators is broken down into radiated and conducted emissions (CE). These conducted emissions fall into two categories: common mode (CM) noise and differential mode (DM) noise.

Knowing where the CM noise and DM noise appear in the CE spectrum enables power supply designers to effectively apply EMI suppression techniques, which saves design time and bill of material (BoM) costs.

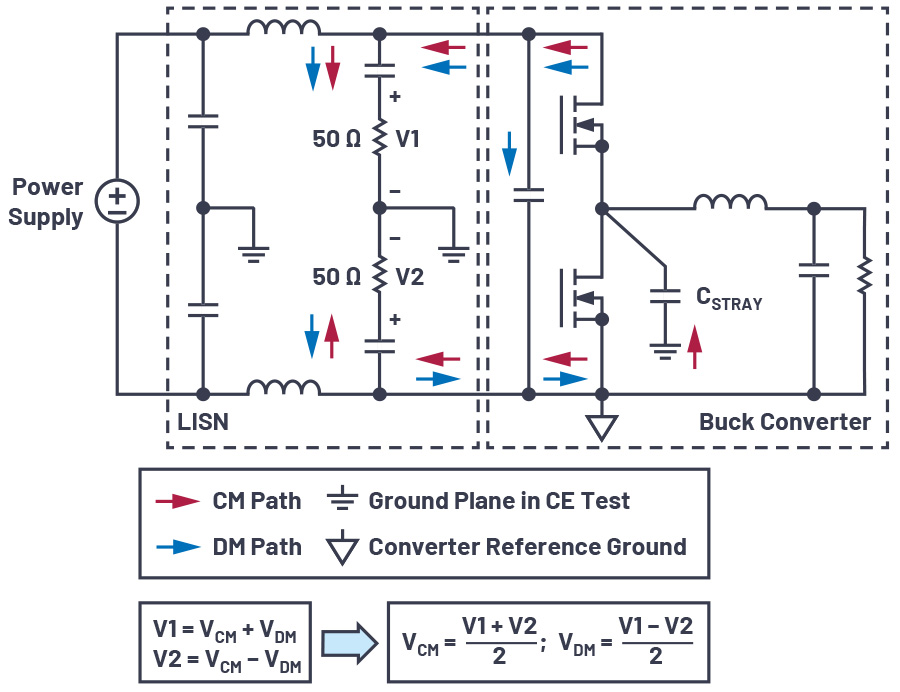

Figure 1 shows the CM noise and DM noise paths for a typical buck converter. This example uses an LTC7818 controlled switching regulator. DM noise is produced between the supply line and the return line, while CM noise is produced between the supply lines and the ground plane (such as a copper test table) via stray capacitance, CSTRAY. The LISN for CE measurement is placed between the power supply and buck converter. The LISN itself cannot be used for direct measurement of CM and DM noise, but it does measure supply and return supply line noise, V1 and V2 in Figure 1, respectively. These voltages are measured across 50Ω resistors.

Figure 1: The CM noise path and DM noise path in an LTC7818-controlled switching regulator buck converter

From the definition of CM and DM noise, shown in Figure 1, V1 and V2 can be expressed by the sum and difference of the CM voltage (VCM) and DM voltage (VDM), respectively. This allows us to calculate VCM from the average of V1 and V2, and VDM as half of the difference between V1 and V2.

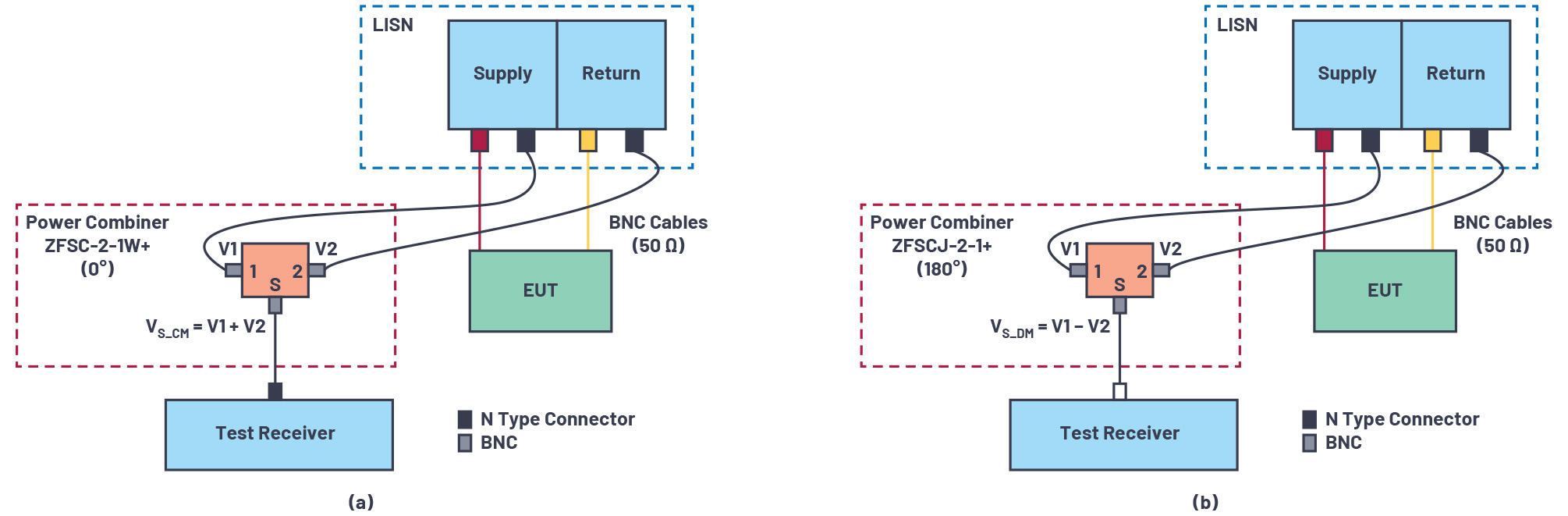

Figure 2: Experimental setup for measuring (a) VCM and (b) VDM

Measuring noise

A T type power combiner is a passive device that combines two input signals to a single port output. A 0° combiner produces a vector sum of the input signals at the output port and a 180° combiner produces a vector difference of input signals.1 Therefore, a 0° combiner can be used to produce VCM and a 180° combiner to produce VDM.

Two combiners were used to measure VCM and VDM from 1MHz to 108MHz. The power combiner is added to the standard CE test setup (Figure 2). The outputs of the LISN for the supply line and return line are connected to Input Port 1 and Input Port 2 of the combiner, respectively. For the 0° combiner, the output voltage is VS_CM = V1 + V2; for the 180° combiner, the output voltage is VS_DM = V1 – V2.

The output signals of combiners VS_CM and VS_DM must be processed in the test receiver to produce VCM and VDM. The power combiners have specified insertion losses compensated in the receiver. Since VCM = 0.5 VS_CM and VDM = 0.5 VS_DM, the test receiver subtracts an additional 6dBµV from the received signal. After compensating for these two factors, the measured CM noise and DM noise are read in the test receiver.

Measurement verification

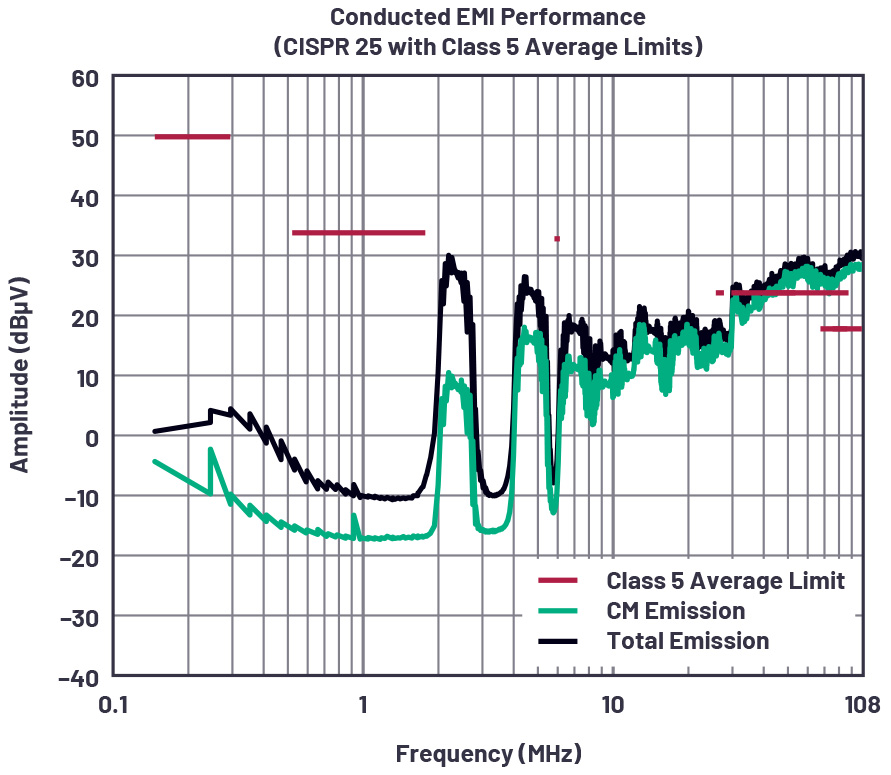

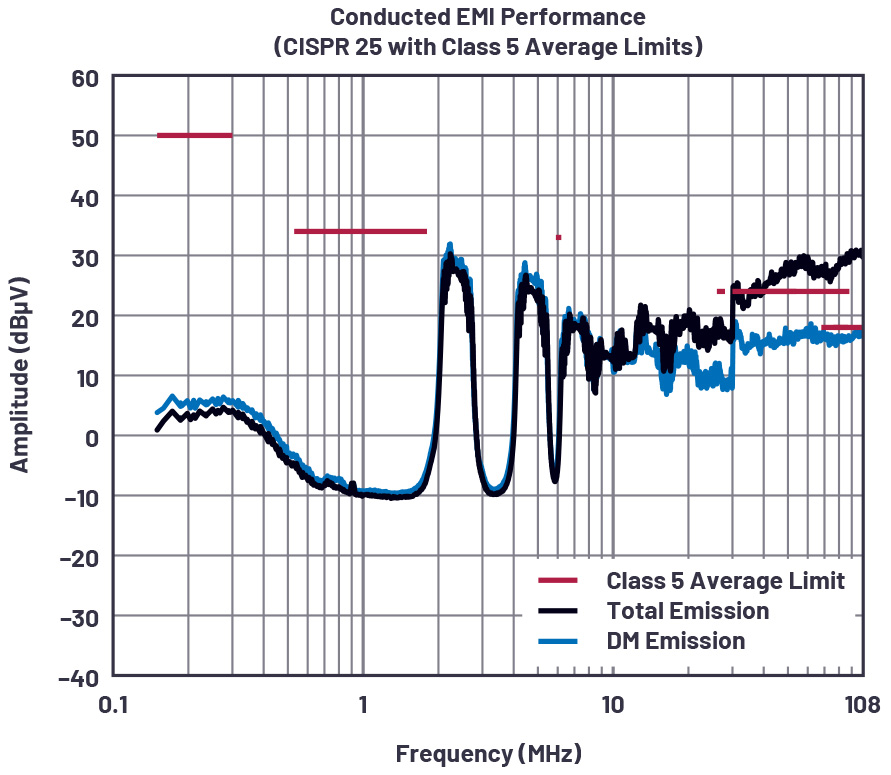

A standard demo board with dual buck converters is used to verify this method. The switching frequency of the demo board is 2.2MHz, while VIN = 12V, VOUT1 = 3.3V, IOUT1 = 10A, VOUT2 = 5V, and IOUT2 = 10A.

In Figure 3, the higher EMI curve shows the total voltage method CE measured with the standard CISPR 25 setup, while the lower emissions curve shows the separated CM noise measured by adding the 0° combiner. In Figure 4, the higher emissions curve shows the total CE, while the lower EMI curve shows the separated DM noise measured by adding the 180° combiner. These test results comply with theoretical analysis, suggesting that DM noise dominates the noise at a lower frequency range, while CM noise dominates at the higher frequency range.

Figure 3: Measured CM noise vs total noise

Figure 3: Measured CM noise vs total noise

Figure 4: Measured DM noise vs total noise

CISPR 25

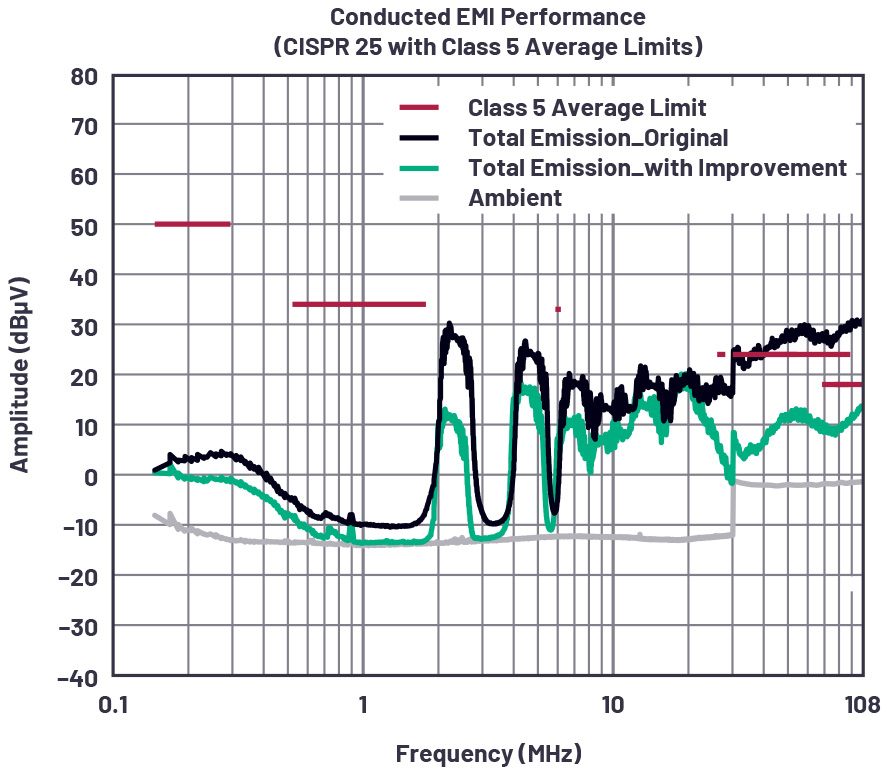

According to the measured results, the total noise emission exceeds the limit of CISPR 25 Class 5 at 30MHz to 108MHz. By separating the CM and DM noise measurements, it appears that the high conducted emissions at this range are caused by CM noise. It makes little sense to add or enhance the DM EMI filter or reduce the input ripple, as these mitigation techniques would not reduce the problematic CM noise at this range.

Methods specifically addressing CM noise are implemented on a demo board. One source of CM noise is high dV/dt signals in the switching circuit. Reducing dV/dt by increasing the gate resistance can decrease the noise level. The smaller the CSTRAY, the lower the CM noise detected in LISN. Reducing the copper area of the switch node reduces CSTRAY and adding a CM EMI filter at the input of the converter obtains high CM impedance, therefore reducing the CM noise into the LISN. By implementing these methods, the noise at 30MHz to 108MHz is reduced enough for compliance with CISPR 25 Class 5.

Figure 5: Total noise with improvement

About the authors:

Ling Jiang is an applications engineer, Frank Wang is an EMI engineer,

Keith Szolusha is applications director and Kurk Mathews is senior applications manager at Analog Devices.