Using a wideband balun with ADCs

Most high-speed ADCs use a differential input structure. This provides good common-mode noise rejection, but often requires a single-ended signal to be converted into a differential signal at the ADC input. A passive balun or transformer and an active amplifier are the main choices for the conversion process. By Ian Beavers, Analog Devices.

While many high-performance components are available for this part of the system, even the best solutions embed small differential imbalances that distort the signal and decrease the ADC’s Spurious Free Dynamic Range (SFDR).

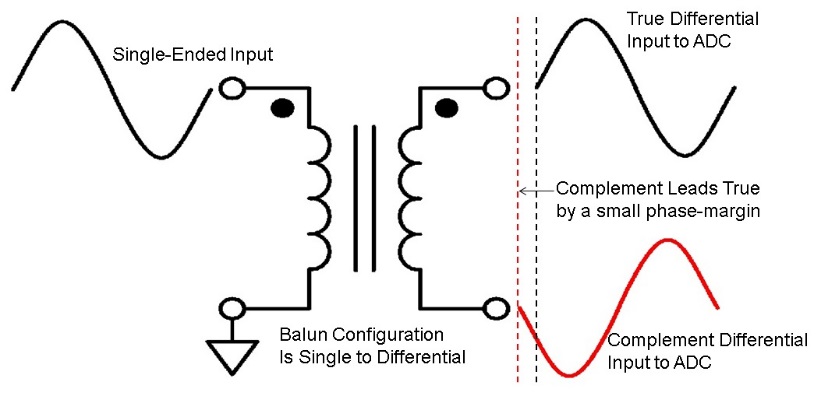

Phase mismatch between each side of the differential input signal at the front-end of the ADC increases the power in the harmonics of the fundamental signal. This can happen when one side of the differential signal leads the other side in time by some amount of phase relative to its period. The effect can be seen in the graphic (below), when one side of a differential pair leads the other side by a small margin of periodic phase.

In this case, a phase mismatch of a few degrees appears on the output of a balun to the differential inputs of the ADC. This can cause the 2nd harmonic to be higher than it would otherwise be if the differential inputs were perfectly matched in phase, thus impacting SFDR.

Another imbalance at the front-end of a differential signal acquisition system can be amplitude mismatch. When one side of a differential signal has a different gain than its complement, the ADC input sees one side as a larger signal and the other as a smaller signal. This otherwise reduces the full power of the fundamental signal and decreases the SFDR in dBc. A 2dB amplitude mismatch between differential inputs will result in a 1dB full scale reduction in power of the input signal. Each of these front-end signal integrity issues has the potential to degrade the SFDR of the ADC as well as the signal deciphering capability of the total system.

For a well-designed monolithic ADC core, the SFDR will typically be dominated by the dynamic range between a carrier frequency and the 2nd or 3rd harmonic of the fundamental frequency of interest. A balun with a high phase or amplitude mismatch can amplify the harmonics in an FFT of an otherwise high performance ADC.

|

Author Profile: Ian Beavers, a staff engineer for the Digital Video Processing Group at Analog Devices (Greensboro, NC), is a team leader for HDMI and other video interface products. With over 15 years’ experience in the semiconductor industry, he has worked for ADI since 1999. He holds a bachelor’s degree in electrical engineering from North Carolina State University and an MBA from the University of North Carolina at Greensboro. |