LCD display controller supports wide range of resolutions

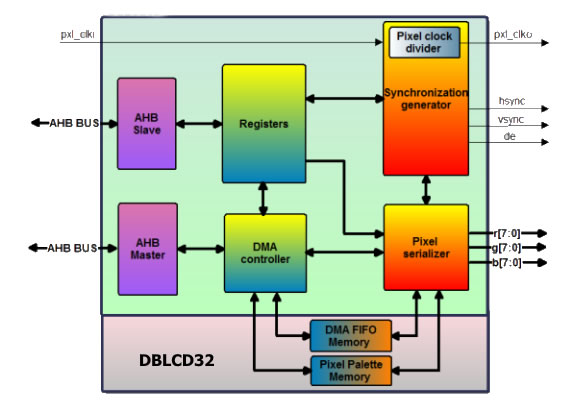

An IP Core has been introduced by Digital Core Design - the DBLCD32 IP Core is a fully configurable, universal LCD/TFT display controller, which supports a range of resolutions. Moreover, it enables both, horizontal and vertical parameters’ synchronisation setup. The DBLCD32 IP Core is a fully configurable, universal LCD/TFT display controller.

It supports a wide range of resolutions and enables both, horizontal and vertical synchronisation parameters setup. The display’s pixel clock can be generated by an internal pixel clock divider based on the bus clock, or delivered to the core by a dedicated pin.

"Additionally, an engineer can use an externally generated pixel clock" explained Tomasz Krzyzak, Vice President of DCD. "Its polarisation, as well as synchronisation signals, is fully configurable."

The DBLCD32 has been also equipped with a DMA capable master interface, which can be used to access a framebuffer, when placed directly in a system memory. Embedded DMA controller has a configurable FIFO to store pixels data, which increases system throughput and performance.

"The transmission on the master interface is burst oriented and there is a possibility of defining the burst size limit," added Krzyzak.

Data fetched by the DMA interface can be translated to 24-bits RGB signals, depending on the selected colour mode. There are three standard colour modes supported: 24-bits True Colour, 16-bits(5-6-5) High Colour and 8-bits index colour mode. Additionally, a 32-bit True Colour is also supported, but the MSB byte of each four byte word is ignored. In case of the Indexed Colour Mode, the DBLCD32 is equipped with pixel palette RAM, which is used to translate each byte from the display buffer into 24-bit RGB output. There are two different formats of colour palettes available. The core supports the page flipping mechanism, which enables the usage of multiple buffering without the tearing effect.

The DBLCD32 also incorporates a set of programmable interrupts available related to both display synchronisation and DMA status signals. The core is capable to work on both little and big endian systems. To increase the system performance and flexibility of usage, the DLBLCD32 can be config-ured in two possible optimisation levels, to find a proper balance between a gate count and a critical path length.

Key features:

- 24-bit RGB interface

- Configurable display resolution

- Configurable horisontal sync length and blanking

- Configurable vertical sync length and blanking

- Configurable RGB signals polarisation

- Configurable pixel clock polarisation

- Internal pixel clock divider

- Different pixel clock modes

- DMA capable interface

- Configurable DMA FIFO

- Configurable burst size limit

- AHB bus interface (32-bit)

- 24-bit True Colour mode support

- 16-bit (5-6-5) High Colour mode support

- 8-bit Indexed Colour mode support

- 32-bit True Colour mode support (one byte ignored)

- Pixel palette RAM

- Page flipping support

- Programmable interrupts

- Big and little - endian support

- Two different optimisation levels

- Fully synthesisable, synchronous design.