Platform ushers in a new era of emulation

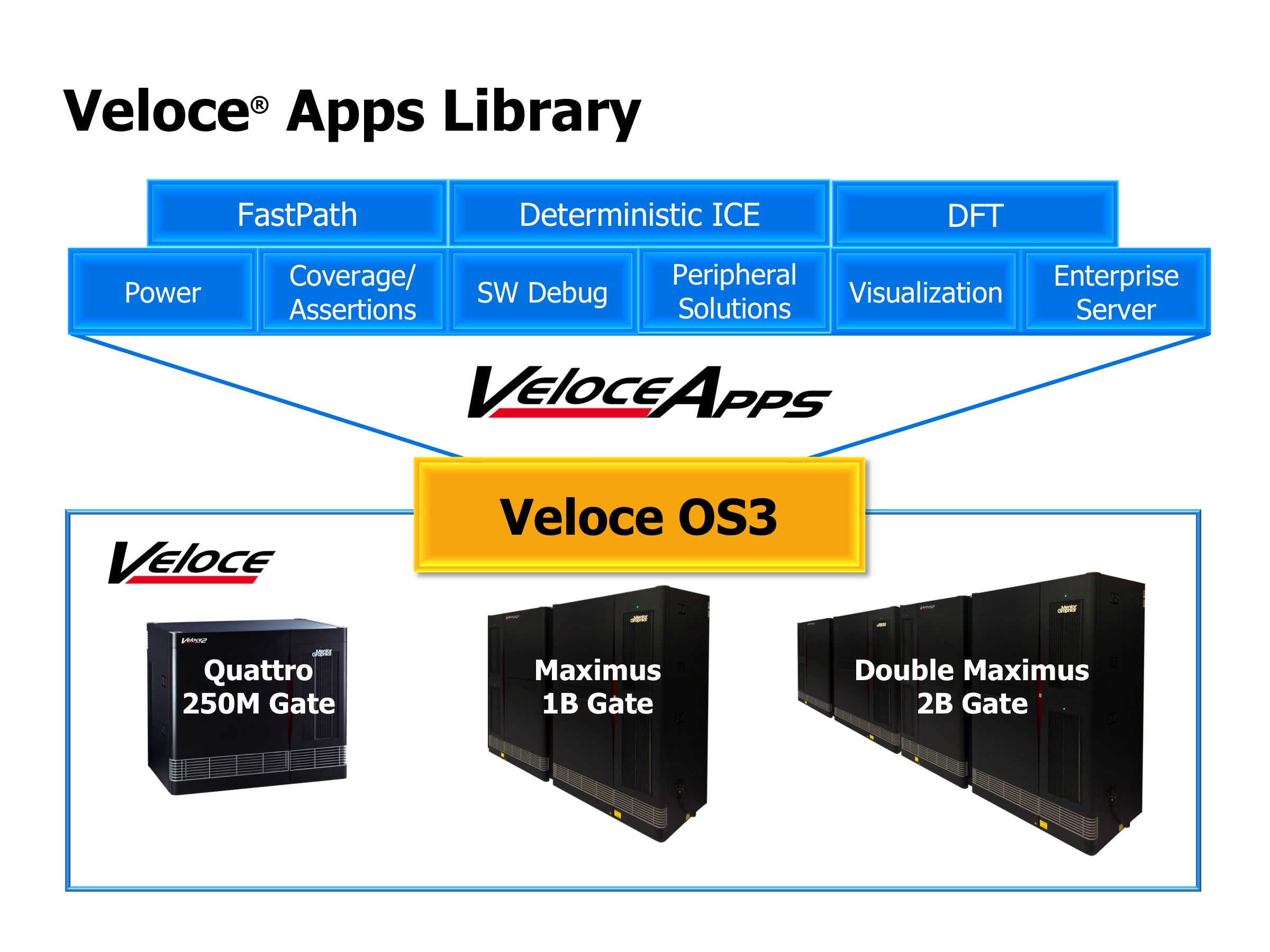

Announcing new applications for the Veloce platform, Mentor Graphics has ushered in a new era of emulation. The new apps - Veloce Deterministic ICE, Veloce DFT and Veloce FastPath - overcome critical system-level verification challenges in complex SoC and system designs. They run on an upgraded Veloce OS3 operating system that significantly accelerates design compile cycles, gate-level flows and the time it takes to review results. The combination of Veloce Apps on Veloce OS3 puts more capabilities into the hands of more engineers more quickly than hardware-centric strategies.

Each of the new Veloce Apps addresses a specific verification issue:

- Veloce Deterministic ICE overcomes unpredictability in ICE environments by adding 100% visibility and repeatability for debug, and provides access to other ‘virtual-based’ use models;

- Veloce DFT accelerates Design for Test (DFT) verification prior to tape-out to minimise the risk of catastrophic failure, and significantly reduces run times when verifying designs after DFT insertion; and

- Veloce FastPath optimises emulation performance when verifying large multi-clock SoC designs by enabling faster model execution speed.

These new apps join Veloce Power, Veloce Enterprise Server and other apps in an expanding arsenal of software innovations for the Veloce emulation platform. Mentor will continue to expand the library of Veloce Apps to introduce new ways to ensure designs meet their functional and performance specifications on schedule.

The Veloce OS operating system adds software programmability and resource management to the Veloce platform, making it easier to add new use models that increase the ROI of the emulator. The recent upgrade of Veloce OS3 covers several innovations:

- Integration of new high performance computing platforms cuts compile time by 50%;

- A faster gate-level flow operates as plug & play - able to accept flat or hierarchical designs. This flow reduces the amount of memory needed for compilation, which improves performance. By making it easier to load and verify gate-level designs, the new flow improves confidence in silicon fidelity; and

- The combination of software and hardware improvements spanning the run time and debug cycles achieves 200% faster time-to-visibility.

These new Veloce emulation capabilities demonstrate how innovative software, running on powerful, qualified hardware and an extensible operating system, can target design risks faster than hardware-centric strategies. As emulation enters its fourth decade and expands across mainstream markets, the Veloce emulation platform has become a powerful resource across a range of hardware, software and system verification flows.

Eric Selosse, Vice President and General Manager, Emulation Division, Mentor, commented: "Mentor continues to demonstrate its technology leadership through its application-based strategy for the Veloce emulation platform. These latest innovations accelerate overall verification throughput performance for our customers. The focus on software apps for specific SoC and system-level challenges is driving the future of emulation.”