Neural network DSP IP core for automotive applications

Cadence Design Systems has unveiled the Cadence Tensilica Vision C5 DSP, which it claims to be the industry’s first standalone, self-contained neural network DSP IP core optimised for vision, radar/lidar and fused-sensor applications with high-availability neural network computational needs. Targeted for the automotive, surveillance, drone and mobile/wearable markets, the Vision C5 DSP offers 1TMAC/sec computational capacity to run all neural network computational tasks.

As neural networks get deeper and more complex, the computational requirements are increasing rapidly. Meanwhile, neural network architectures are changing regularly, with new networks appearing constantly and new applications and markets continuing to emerge. These trends are driving the need for a high performance, general-purpose neural network processing solution for embedded systems that not only requires little power, but also is highly programmable for future-proof flexibility and lower risk.

Neural network DSP vs. a neural network accelerator

Camera-based vision systems in automobiles, drones and security systems require two fundamental types of vision-optimised computation. First, the input from the camera is enhanced using traditional computational photography/imaging algorithms. Second, neural-network-based recognition algorithms perform object detection and recognition. Existing neural network accelerator solutions are hardware accelerators attached to imaging DSPs, with the neural network code split between running some network layers on the DSP and offloading convolutional layers to the accelerator. This combination is inefficient and consumes unnecessary power.

Architected as a dedicated neural-network-optimised DSP, the Vision C5 DSP accelerates all neural network computational layers (convolution, fully connected, pooling and normalisation), not just the convolution functions. This frees up the main vision/imaging DSP to run image enhancement applications independently while the Vision C5 DSP runs inference tasks. By eliminating extraneous data movement between the neural network DSP and the main vision/imaging DSP, the Vision C5 DSP provides a lower power solution than competing neural network accelerators. It also offers a simple, single-processor programming model for neural networks.

“Many of our customers are in the difficult position of selecting a neural network inference platform today for a product that may not ship for a couple of years or longer,” said Steve Roddy, Senior Group Director, Tensilica marketing at Cadence. “Not only must neural network processors for always-on embedded systems consume low power and be fast on every image, but they should also be flexible and future proof. All of the current alternatives require undesirable tradeoffs, and it was clear a new solution is needed. We architected the Vision C5 DSP as a general-purpose neural network DSP that is easy to integrate and very flexible, while offering better power efficiency than CNN accelerators, GPUs and CPUs.”

“The applications for deep learning in real-world devices are tremendous and diverse, and the computational requirements are challenging,” said Jeff Bier, founder of the Embedded Vision Alliance. “Specialised programmable processors like the Vision C5 DSP enable deployment of deep learning in cost- and power-sensitive devices.”

Vision C5 DSP features and performance

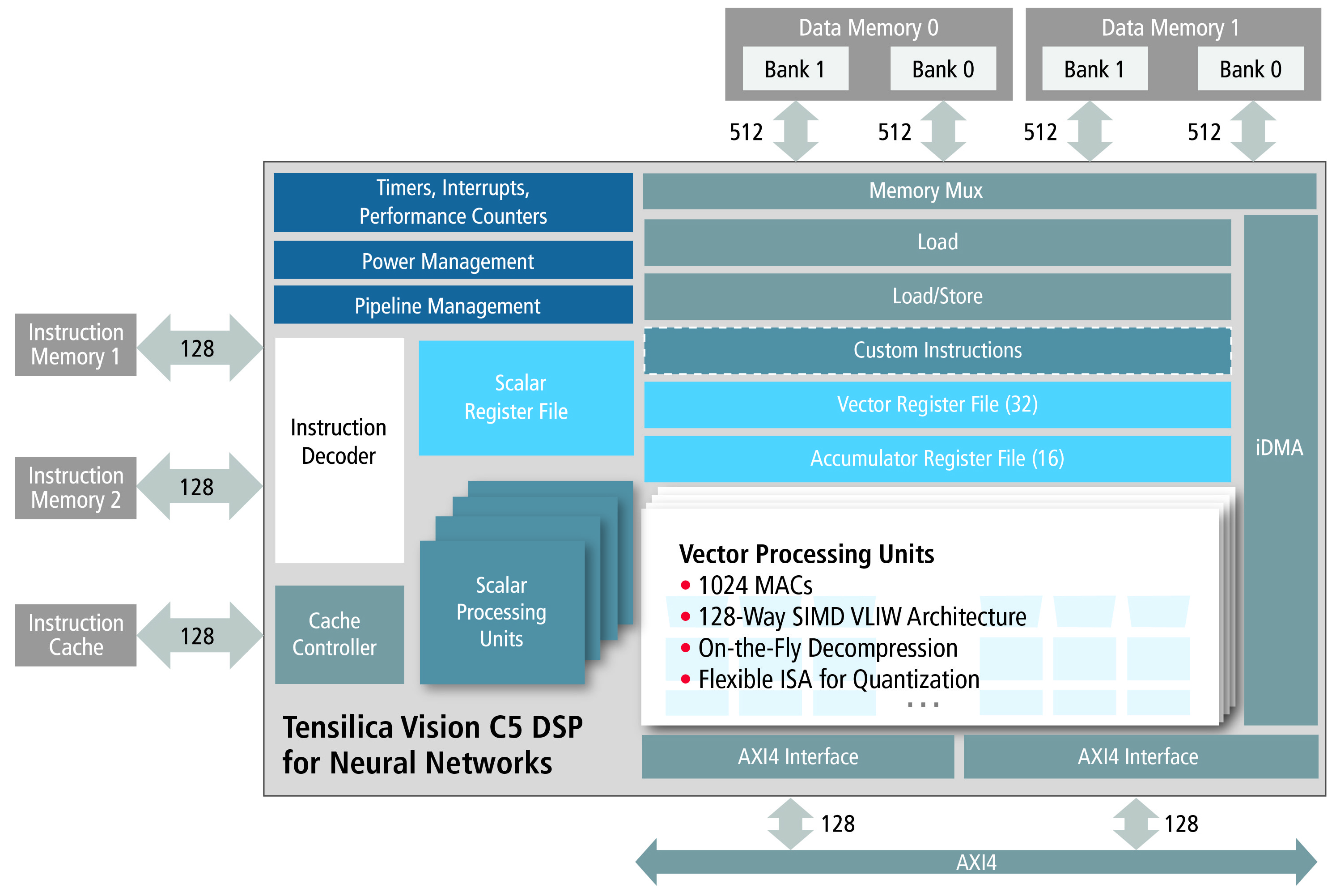

The Vision C5 DSP offers neural network performance in a self-contained engine:

- 1TMAC/sec computational capacity (four times greater throughput than the Vision P6 DSP) in less than 1mm2 silicon area provides high computation throughput on deep learning kernels

- 1024 8-bit MACs or 512 16-bit MACs for performance at both 8-bit and 16-bit resolutions

- VLIW SIMD architecture with 128-way, 8-bit SIMD or 64-way, 16-bit SIMD

- Architected for multi-core designs, enabling a multi-teraMAC solution in a small footprint

- Integrated iDMA and AXI4 interface

- Uses the same proven software toolset as the Vision P5 and P6 DSPs

- Compared to commercially available GPUs, the Vision C5 DSP is up to six times faster in the well-known AlexNet CNN performance benchmark and up to nine times faster in the Inception V3 CNN performance benchmark

The Vision C5 DSP is a flexible and future-proof solution that supports variable kernel sizes, depths and input dimensions. It also accommodates several different coefficient compression/decompression techniques, and support for new layers can be added as they evolve. In contrast, hardware accelerators provide a rigid solution because of more limited re-programmability.

The Vision C5 DSP also comes with the Cadence neural network mapper toolset, which will map any neural network trained with tools such as Caffe and TensorFlow into executable and highly optimised code for the Vision C5 DSP, leveraging a comprehensive set of hand-optimised neural network library functions.