Metal cases add value in space electronics

Does the design of space electronics have room for traditional metal case devices? As a proven packaging option, the appeal of compliance and reliability has designers taking a new look at heritage technology. Even as hermetic devices have been popular design choices over the last few decades, today designers are revisiting Transistor Outline (TO) JEDEC packages that were once the norm for space electronics.

Back to the future with TO technology

Ceramic material made up most circuit boards in the early days of space design, with commercial missions and the New Space generation requiring the use of FR4 board materials. Some concerns arise with the attachment of large-scale surface mount parts; for example ESA who have instructed that component suppliers must ensure CTE compliance when these designs are employed within Class 1 boards (i.e., glass fibre epoxy or glass fibre polyimide resins), this is now a caution in the organisation’s Space Product Assurance Classification ECSS-Q-ST-70-38C.

Lower mass advantage can be achieved with packages such as UA and UB, however careful soldering of the devices adds risk and is a technically challenging process. Packages such as SMD-05 and SMD-1 are also susceptible to failures due to their larger mass and surface areas. Stress fractures may occur along joint areas, creating a tangible risk of catastrophic failure and an unplanned end to the mission.

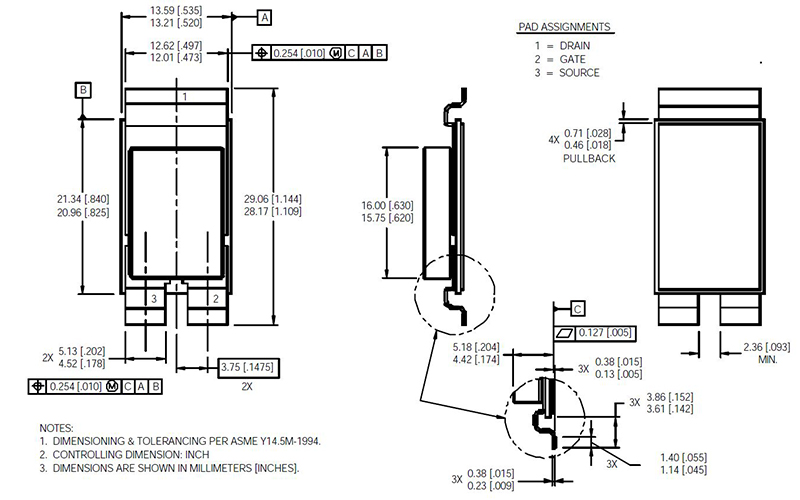

SMD packages may also crack if mounted above a large ground plane and subjected to extensive thermal cycles, common in space electronics. One potential solution to this widely recognised problem is illustrated in the figure below, depicting a CTE compliant mounted package or carrier featuring dual lead connections.

Proven metal case transistors offer a contrast, with a greater level of reliability and some degree of compliance. For example, the device’s leads function as an expansion route in the case of thermal shocks Heat is more effectively dissipated within the system, based on accelerated switching of applications and smaller chips that reach the boundaries of their respective controls.

Finding long-term value in upgradability

Metal case transistors are also more easily upgradable than surface mount options. The plastic TO-220 package provides as example, offering a footprint identical to that of the TO-257. Early prototyping can rely on lower cost components and can then evolve to more robust packaging for production.

As cost-consciousness drives the New Space industry, applications such as higher volume satellite constellations in low earth orbit can see a strong competitive advantage.

Ideally, semiconductor manufacturers will continue to provide a choice of components and test routing that includes TO packaging and surface mount options – both compliant to Mil standards or ESA specifications.

Screening options such as NS1 and NS2 play a role as well, assuring cost effective reliability. The NS1 sequence provides traceability to all materials and operations, ensuring manufacture is based on robust, controlled, space-proven processes and designs. NS2 processes provide the next level of assurance, by incorporating baseline mechanical and electrical screening.

Designers have a new opportunity to innovate with heritage technology – tapping into compliant, reliable options to mix technologies or manufacturers’ die within the package.