Integrity tool targets high-speed PCB designs

A Signal Integrity/Power Integrity (SI/PI) product, developed for high-speed PCB designs, has been released by Mentor Graphics. The HyperLynx addresses high-speed systems design problems throughout the design flow, starting at the earliest architectural stages through to post-layout verification.

With the increased complexity and high-speed performance of today’s ICs, a growing number of PCBs suffer from signal degradation and timing problems which are exacerbated by power delivery issues. This impacts board performance and logic, requiring costly redesign.

The SI/PI product provides tools for pre- and post-layout signal integrity, timing, crosstalk and power integrity analysis to quickly generate accurate simulation results and prevent design re-spins. Features include power-aware IBIS model support and the DDRx wizard for DDR4/LPDDR4 validation.

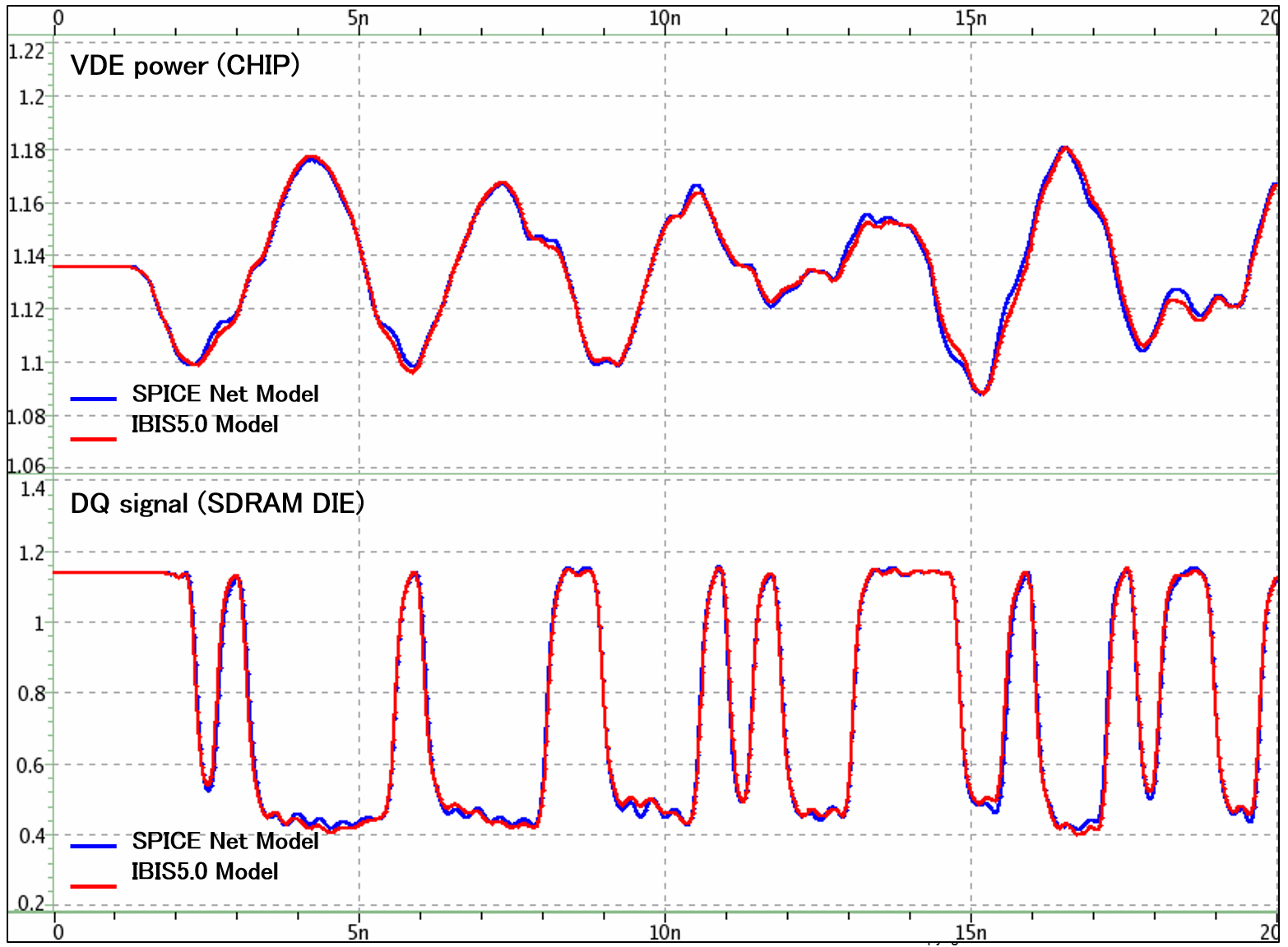

The HyperLynx supports IBIS v5.0 models for ICs that represent non-ideal power effects. This capability accurately models supply currents, including pre-driver effects, switching slowdown due to sagging supply voltage, and better buffer capacitance modelling. Power-aware IBIS modelling can be used in all simulation types, including DDRx analysis, to study the power effects of timing and signal quality. This tool can model simultaneous switching noise, critical for designing next-gen memory interconnects.

Supporting the latest JEDEC standards, the DDRx Wizard verifies all DDR memory types, including DDR4 and its low-power (LPDDR4) counterparts. The DDRx Wizard can produce eye diagrams for complete verification of DDR3 and next-gen DDR4 memory systems. Each individual bit in the simulation is validated using eye-based metric checks, including integrated timing analysis for DDRx and LPDDRx.

“Socionext is addressing SI/PI issues that get more complicated at higher frequencies. Over 2Gb/s, simultaneous switching noise must be considered when designing and simulating DDR4 circuits. We are working with our customers and partners to address this challenge, and collaborating with Mentor Graphics to develop a HyperLynx DDR4 simulation kit,” said Takayuki Tsuru, Director, Custom SoC Business Unit, SoC Product Solution Department, Socionext. “With our IBIS5.0 modelling technique and the HyperLynx power-aware SI solution, we achieved a 95% reduction in simulation time with excellent correlation to transistor-level simulation. The simulation kit is available for high performance server and storage applications, and we are also developing a LPDDR4 design kit for low power mobile devices. We believe our customers and Socionext will be able to continuously improve design efficiency and decrease development costs with Mentor Graphics’ global support.”

“Our HyperLynx SI/PI product continues to serve the high-speed demands of today’s most advanced systems designs,” commented A.J. Incorvaia, Vice President and General Manager, Systems Design Division, Mentor Graphics. “Our new power-aware modelling technology enables our customers to quickly and accurately simulate complex signalling protocols, saving them substantial time and cost.”

The HyperLynx SI/PI product for ‘power-aware’ high-speed design is available now. To accelerate time-to-market using the HyperLynx, visit the HyperLynx Alliance, a cloud-based learning centre which includes free virtual labs. The virtual lab series leverages partner models and reference designs with the HyperLynx to demonstrate suitable design methodologies that address difficult high-speed PCB SerDes and DDR design challenges.