Emulation takes on post-silicon validation

According to a study jointly carried out by Mentor Graphics and Wilson Research Group in 2014, at least one percent of bugs escape to silicon level, and that underscores the critical importance of post-silicon validation. Moreover, there simply aren’t enough verification cycles to find bugs that pass the pre-silicon phase.

Author: Jean-Marie Brunet, Marketing Director, Emulation Division, Mentor Graphics

The traditional verification flows are now beginning to reach their limitations by the time designs get to the post-silicon stage. In other words, the gap between pre-silicon verification and post-silicon validation is a serious challenge, especially for compute-intensive, System-on-Chip (SoC) designs.

For debugging at efficient speeds in large and complex SoC designs, there is an increasing need to effectively connect pre- and post-silicon debug environments. That requires a convergence path between the two worlds.

Within the last year, emulation has made moves to play a bigger role in bridging the gap between pre-silicon verification and post-silicon validation. Case in point: Mentor Graphics is moving its emulation tool (the Veloce emulation platform) toward post-silicon validation with an integration with Ixia’s IxVerify virtual test tool.

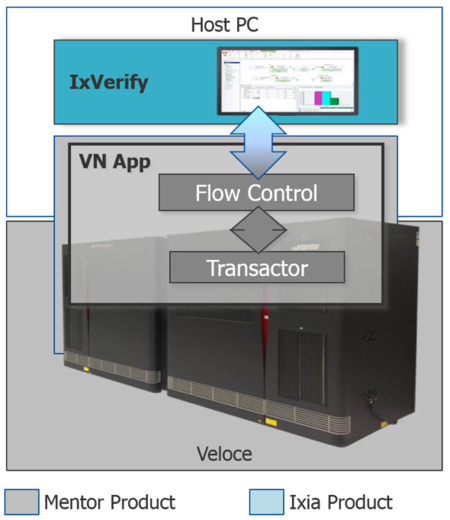

Mentor’s move to scale its virtual emulation platform into the lab settings is a testament to how verification cycles vary at the pre- and post-silicon stages. Mentor Graphics has integrated Ixia’s IxNetwork Virtual Edition (VE) family of testers - called IxVerify - as the emulation front-end to its Veloce Virtual Network (VN) App at the back-end. The partnership with Ixia helps Mentor create a 'shift-left' impact in the verification flow and thus bridge the gap between pre- and post-silicon stages in networking chipset designs.

Veloce VN App bridges the gap between pre-silicon verification and post-silicon validation in networking SoCs by integrating the IxVerify virtual test tool with the Veloce emulation platform.

IxVerify is a virtual test tool for networking SoC designs that can run hundreds of virtualised test ports at once. Hence, it can dynamically shape traffic and thus ensure zero packet loss at maximum emulation speeds.

The Veloce VN App allows networking SoC design teams to run the same tests in simulation, emulation and lab environments for rapid design debug and faster time-to-market. So, a bug discovered in the lab can also be traced in emulation flow using the same test environment in the lab.

The rising mask costs at smaller nodes are winning much of the media limelight. However, the real prize here is time-to-market, which can significantly boost revenue streams of electronic devices.