Reference Designs

Wideband Receiver Reference Design for Upstream DOCSIS 3.1 Applications

Texas Instruments

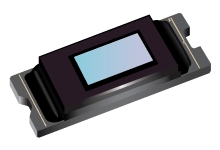

This reference design consists of an analog front-end (AFE) signal chain for wideband receiver applications using the LMH2832 digitally controlled variable gain amplifier (DVGA) and ADS54J40 analog-to-digital converter (ADC). The design is primarily targeted for upstream DOCSIS 3.1 receiver applications specified for cable modem termination systems (CMTS) and supports up to 196 MHz of upstream signal bandwidth. The circuit solves the filtering and analog signal processing requirements for the DOCSIS 3.1 standard: which makes it easier for system designers to readily incorporate the design on the CMTS-side of the upstream signal path.

Features

- AC-coupled signal path from 100 kHz to 204 MHz with 196 MHz of upstream-signal-bandwidth support for DOCSIS 3.1 applications58 dBFs of minimum system SNR (200 MHz BW) for –1-dBFs input at the ADC70 dBFs of minimum system SFDR for –1-dBFs input at the ADC1.71 A of average active-state current consumption on 5-V nominal wall mount power supplyOutput data rate of four lanes per ADC at 5.0 Gbps with JESD204B interface subclass-1 support

Applications

- Modem (cable/DSL/GFAST)

- STB & DVR

- Gateway (xDSL/cable)

Product Categories

- Amplifiers