On the road to software defined power architecture

Software defined power architecture is increasingly being seen as the future for advanced board power management to bring energy efficiency and power-optimised capabilities in datacomms and networking applications by 2020, says Patrick Le Fèvre, Ericsson Power Modules.

Online data services are driving the growth of ICT, with increased traffic requiring networking routers and servers to handle huge amounts of data, which in turn require high-performance multi-core IP processors, ASICs, FPGAs and other digital processing ICs. Modern, leading-edge processors need to adjust voltage to optimise configuration from 0.6 to 1.8V, with a response to meet load step transients.

Digital power

Digital power is a key technology to improve conversion efficiency, especially in ICT applications. Digital DC/DC converters can adapt to changes in line and load conditions, due to network traffic demand for example, in real time. Digital power can also help with the sheer number of different voltage rails required for microprocessors, ASICs, FPGAs and other digital logic.

Digital power is something of a misnomer, as much of a digital power supply mirrors analogue best practice and uses mostly similar or identical components in key areas, such as the power switches and output filter. Fundamentally the difference is represented by the inner control loop changes to implement digital’s flexible methodology via its PMBus-based measurement-and-control sub-system.

Digital power has moved from the early-adopter phase, with many companies using digital power functionalities for testing, set-up and board configuration.

Concept

A further evolution is Software-Defined Power Architecture (SDPA). Today it is only a concept, but it has the potential to bring truly energy-efficient and power-optimised, board-level capabilities in advanced network applications. In this vision, advanced processors will use software command control to adjust required power levels. They will be able to deliver high power when computing operations are at full capacity, or adapt performance and behavioural characteristics to reduce overall energy consumption when a processor is in standby mode, or is only handling limited computational tasks when the data traffic demand is low.

SDPA is likely to include key energy-saving concepts that have been developed over the past few years, such as the dynamic bus voltage, adaptive voltage scaling, fragmented power distribution and classic power technologies such as phase spreading.

SDPA technologies

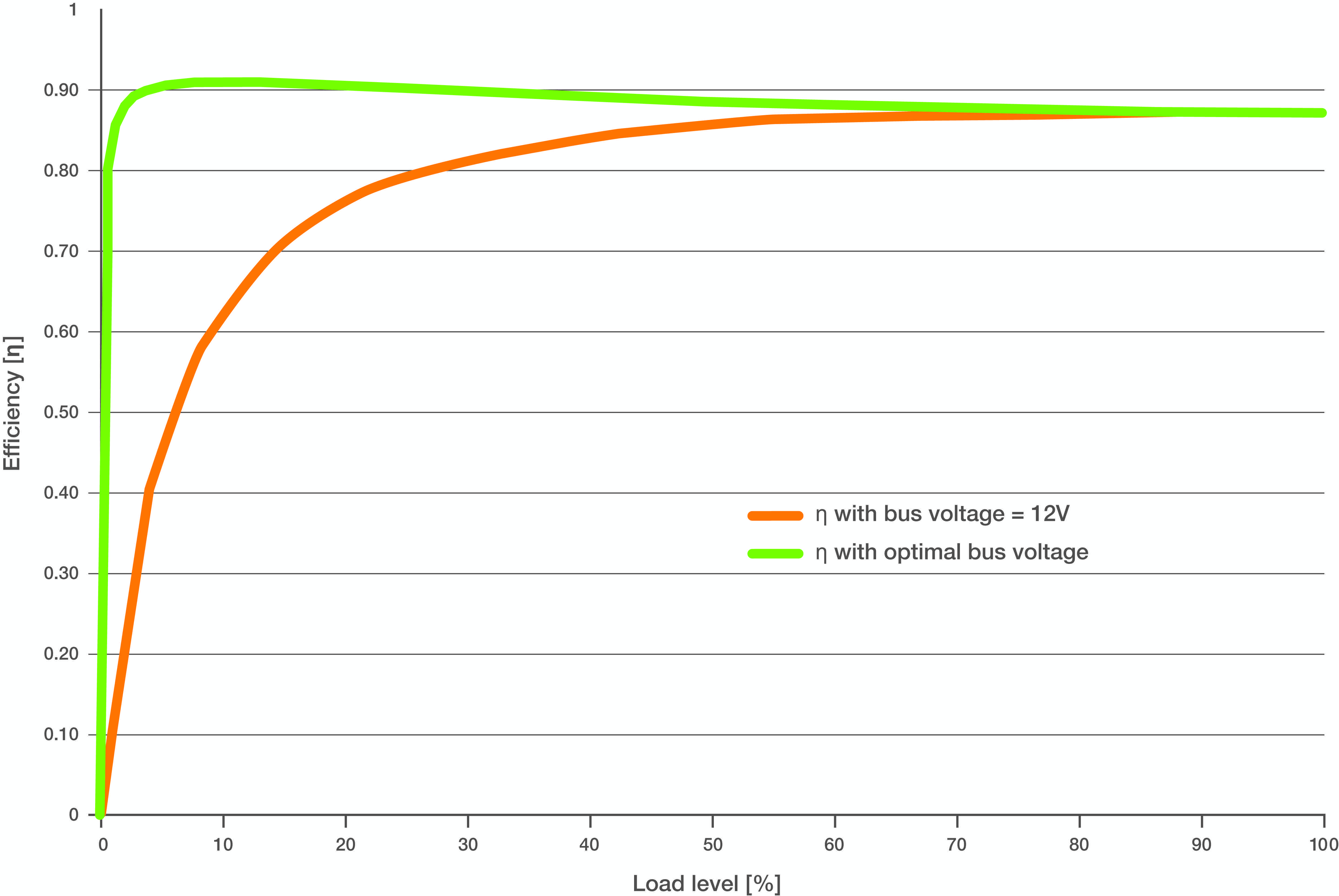

The first of these is the Dynamic Bus Voltage (DBV), an evolution of the Intermediate Bus Architecture (IBA), which is commonly used in datacomms today. The IBA employs Intermediate Bus Converters (IBCs) to convert the traditional 48V DC distribution-level power line down to a static 12 to 14V DC supply line typically. This first ‘down-conversion’ level feeds a number of DC/DC PoL regulators, which supply the final load voltages at the required supply levels for processors and other logic devices. The choice of 12/14V DC ensures a high enough voltage to deliver all the power required by the load in times of high data traffic. This approach becomes highly inefficient when the traffic demand is low. Employing a DBV-based architecture provides the possibility to dynamically adjust the power envelope to meet load conditions. It achieves this by adjusting the intermediate bus voltage, previously a 12/14V DC fixed bus voltage, via advanced digital power control and optimised hardware, combined with a series of software algorithms to deliver higher conversion efficiencies. This can lead to reductions in both energy consumption and power dissipation, which in turn contributes to a reduction in the amount of required cooling. Data from Ericsson suggests that the DBV can reduce board power consumption by between three and 10%, depending on the application.

The second technology is Adaptive Voltage Scaling (AVS), which is a powerful technique to optimise supply voltages and minimise energy consumption in modern high-performance microprocessors. AVS employs a real-time closed-loop approach to adapt the supply and meet the minimum voltage required for the actual clock frequency and workload of the individual processor. It also adjusts to automatically compensate for process and temperature variations in the processor. High-performance microprocessors will change workload and operating conditions within nanoseconds, therefore real-time regulation of the microprocessor supply puts a high demand on the control-loop bandwidth and requires close monitoring of computing hardware performance in the feedback loop.

A third technology is phase spreading, commonly used in systems with multiple switching products to introduce a delay in the switching phase between products. This reduces effects such as a large peak current drawn from the input voltage and input capacitance or high levels of radiated emissions due to synchronised edges of the switching frequency.

Ericsson recently presented fragmented power distribution, which implements digital power monitoring and control capabilities to deliver higher levels of efficiency on multi-kW boards. The technology relies on multiple DC/DC converters distributed at strategic locations on the board to create power islands, all communicating via an internal bus (the PMBus or one dedicated to current-sharing applications). It shares and optimises the delivery of power to the loads. Each converter can be a master or slave unit, operating independently or together to deliver full power and depending on where the power is required, allowing the system to perform at the optimum level.

DBV-based architecture dynamically adjusts the power envelope to meet load conditions

The SDPA is also likely to include other technologies, including adaptive power allocation traffic scaling, where voltage levels will be allocated across board-level systems to meet data traffic demands; state-of-operation reporting; or multi-core activation (or deactivation) on demand, which can be implemented within a multi-core processor or via external software to optimise power at the system or board level.

Power profile optimisation is another option as well as on-the-fly system configuration, set remotely or by a network manager.

Transition

The BMR465 DC/DC power module introduction is described by the company as a milestone in the transition to systems that will implement SDPA. The two-phase, 90A digital PoL converter is optimised to power multi-core IP processors. It offers compensation-free performance and the ability to connect modules in parallel to provide up to 360A to advanced network-processors.

The goal to bring about the SDPA has already been set for 2020, to meet the rollout of 5G technologies. To make this vision a reality, there will need to be significant collaboration between major power system developers, including semiconductor and processor vendors, power module makers and board designers at end customers working in the ICT and networking sectors.

PCIM 2015: Hall 9 - 242