RFEL launches Fractional Rate Resampler IP core at EW Europe

RFEL will be launching its latest core at EW Europe. The Fractional Rate Resampler IP core, which was originally part of the company's multi-award winning ChannelCore Flex product, is now offered as a stand-alone IP core for FPGAs in response to customer requests.

The core enables input data rates to be modified to manage systems with multiple clock domains, unifying all signal paths onto a single clock domain. Arbitrary input data rates can be easily matched to support the data rates required for following algorithms such as DEMODS or CODECs. Equally, the core can be used in post filtering applications so that data rates can be optimally set to match the data rate to the output bandwidth.

This makes the core suitable for Digital Signal Process systems development, harmonising over multiple clock domains, clock domain crossing and algorithm integration that are particularly useful for COMINT, SIGINT, Electronic Warfare (EW), radar, sonar and similar security and surveillance applications.

The architecture uses an Interpolator followed by a Low Pass Filter and a final Decimator stage, leading to the output. This enables the core to change the sample rate of a signal by an integer ratio of L/M, where L is the up-sampling interpolator factor and M is the down-sampler decimator factor. The core can be built as a static configuration (with fixed L and M values) or as run-time programmable variant (where the values for L and M can be modified in real-time). The architecture has an arbitrary internal parallelism and so can support data rates that are limited only by the resources of the FPGA that it is running on. Other key features are a complex wideband input, a high-performance filtering stage and variable bit widths.

RFEL's Fractional Rate Resampler is available as an evaluation core that allows users to integrate the solution into their wider designs for assessment. The evaluation core operates for 30 minutes, before requiring FPGA reconfiguration and can be simply upgraded to the full version by the purchase of a licence key. It is available to target Xilinx and Altera FPGAs.

Dr Alex Kuhrt, RFEL's CEO, said, "RFEL is leader in the field of providing specialist IP for EW. We are constantly reviewing and improving our portfolio of IP designed for EW applications. This Fractional Rate Resampler is a powerful tool in the EW System Designer's toolkit."

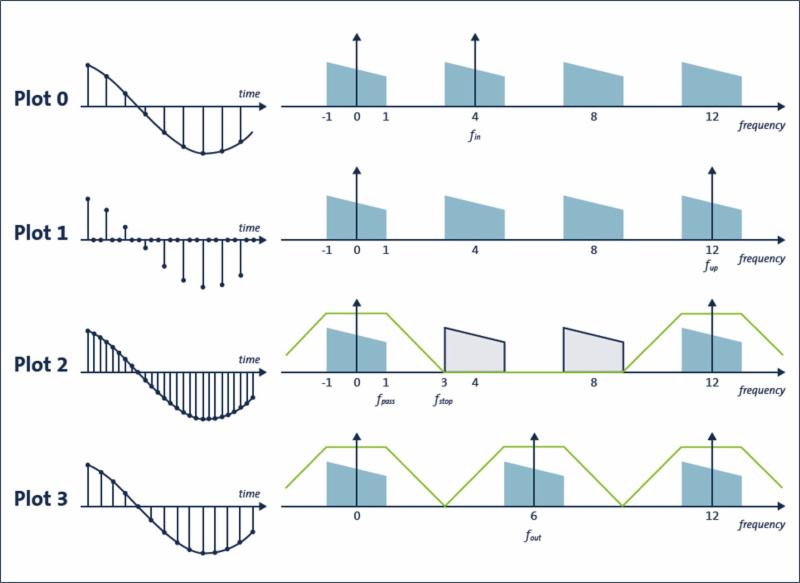

A simple example use case is shown in Figure 1.

Plot 0 shows time and frequency-domain views of the input signal. A section of the infinite sequence of sampling images is shown across the frequency axis at intervals of +/- fin.

Plot 1 shows the input signal after up-sampling by a factor of L=3, achieved by inserting 2 zeros between each input sample.

Plot 2 shows the up-sampled signal after a low-pass filter has been applied. The filter has a frequency response (shown in red) that ensures removal of the greyed-out images.

Plot 3 shows the final re-sampled signal after the up-sampled version has been decimation by M=2.