No boundaries for boundary scan at IPC Apex 2017

JTAG Technologies return to San Diego this year to premiere several new hardware products for PCB testing and In-System [Device] Programming and -to introduce their new collaborative product with Altium – JTAG Maps.

A large number of today's electronic designs feature JTAG/boundary-scan components that provide valuable test resources during hardware debug, manufacturing test and even depot repair.

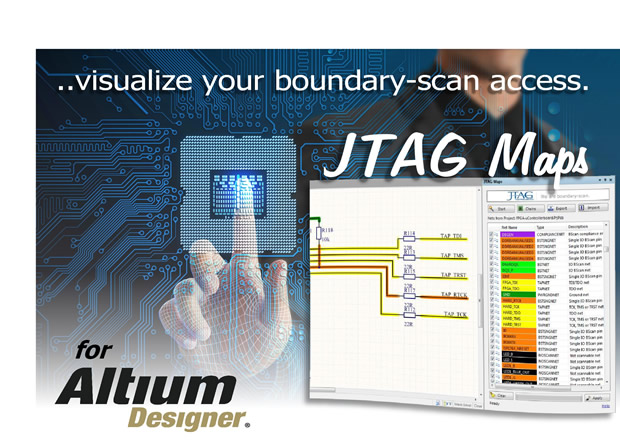

JTAG Maps is a simple extension to the Altium Designer tool suite that allows the user/engineer to thoroughly assess the capabilities of the JTAG/boundary-scan resources on their design - before committing to layout.

Highlighting the schematics

Until now engineers could often spend hours highlighting the boundary-scan nets of a design manually to assess the fault coverage that boundary-scan testing could bring a specific design. Today the free JTAG Maps for Altium, application extension, does all this and more, freeing up valuable time, allowing a more thorough DfT and speeding time to market.

With or without boundary-scan models

Boundary-scan device models (BSDLs) are pivotal to any JTAG/boundary-scan process as they indicate precisely which pins can be controlled or observed by JTAG/boundary-scan. However BSDL models are not always available in a timely manner. To overcome this potential problem JTAG Maps for Altium includes an 'assume scan covered' feature enabling a view of potential boundary-scan coverage without a specific BSDL. This feature can also be used to indicate fault coverage to a connector (set to assume scan covered) or to highlight the differences in fault coverage between two equivalent parts, one with and one without built-in JTAG/boundary-scan.

Automatic chain detection

JTAG Maps for Altium will automatically detect the scan chain path (or paths) with no limits to the number of paths (aka TAPs) in the design. The nets associated with the TAPs will be highlighted separately from the 'testable' nets using different colors.

Import as well as export

While most users will want to simply use the quick coverage report that JTAG Maps for Altium can provide, it is still possible to import a more accurate picture. After exporting a JTAG ProVision project, the data can be sent to your local JTAG Technologies office, Approved Application Provider, or approved JTAG representative for further analysis. A simple message file containing full fault-coverage information can then be read back into JTAG Maps for display/highlighting.

More highlights from JTAG Technologies at San Diego:

JT 5705/FXT multi-function tester

The latest product on display will be an example of JTAG’s ‘fixture embedded’ test technology - the JT 5705/FXT multi-function JTAG tester built into one the small linear series of cassette-based re-configurable fixtures of Everett Charles Technologies (ECT), a world-renowned name in PCB test fixtures and interface. The JT 5705/FXT is a compact, single-board test system that supports analogue measurement and stimulus, frequency measurements, digital I/O, boundary-scan testing and also in-system device programming. Within the fixture multiple JT 5705/FXT tester cards can be mounted on purpose built carriers featuring the ATE industry standard ‘Pylon’ connectors, making test system build a snap.

Emulative testing and programming

New system CTPG-M to increase fault coverage and speed-up testing on designs featuring µProcessors and FPGAs - Building on their Emulative Test & Programming (ETP) technology, that offers access to the emulation modes of µprocessors or the internal IP bus of an FPGA, JTAG introduces an automatic generator for testing connectivity and functionality between a core and all kinds of memory devices and refers to it with CTPG-M. CTPG-M has been developed to overcome many of the issues associated with testing of memory clusters using conventional boundary-scan (IEEE Std 1149.1) techniques.

JTAG-powered PCB tester-programmer the JT 57xx/RMI ‘Combi-System’

A modular concept of a newly designed base-level 19” 1U rack-mount chassis assembly that can house up to four customer-specified modules offering various JTAG (IEEE 1149.x) controllers, digital IO and analogue IO and other measurement features. The modules are either ½ rack or ¼ rack width and are available in different configurations. JTAG will present you the full module range at the show.