Renesas achieves large-scale memory operation

Supplier of advanced semiconductor solutions, Renesas Electronics, has announced that it has successfully confirmed large-scale memory operation in a split-gate metal-oxide nitride oxide silicon (SG-MONOS) process using fin-shaped 3D transistors for use in microcontrollers (MCUs) with on-chip flash memory having a circuit linewidth of 16 to 14nm or finer.

This result follows Renesas’ achievement in December 2016, when it announced its confirmation of operation for what it claims to be the industry’s first SG-MONOS flash memory cells that use fin-shaped transistors. Renesas has demonstrated the operation and reliability of large-scale memory, achieving significant progress towards realising large-capacity flash memories of more than 100MB for use in MCUs of the 16 to 14nm and later generations.

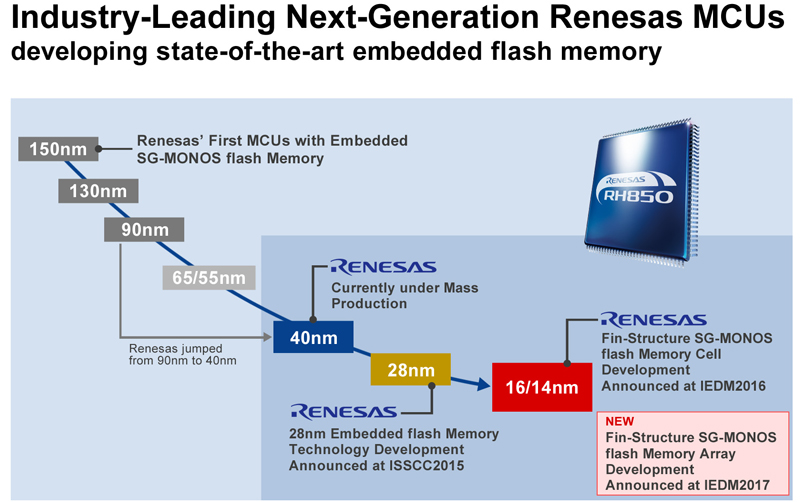

Advances in vehicles especially the autonomous-driving vehicle and progress in the smart society connected by the IoT are accelerating, creating upsurge in demand for advanced high-performance MCUs that make use of even finer design rules to achieve higher performance and lower power consumption. To address this demand, Renesas is developing flash memory that can be embedded in the 16/14nm process generation, which succeeds the 40/28nm processes in which MCUs are currently either being mass produced in or are being developed for. Renesas is now working to achieve further advancement of MCUs by combining high-performance/low-power logic with large-capacity/high-performance nonvolatile memory implemented with finer feature sizes.

In 2016, Renesas announced the successful development of the industry's first fin-type SG-MONOS flash memory cell by applying and adopting charge trap type flash memory technology that had been used in the past. The SG-MONOS flash memory performs its data storage in a thin trap film formed on the surface of the silicon substrate, which makes it comparatively easier to deploy it in a fin structure with a three-dimensional structure. Another feature is that it is highly compatible with 16/14nm logic processes that have the same fin structure. Also, the superlative charge retention characteristics, which are a feature of charge trap type MONOS flash memory, are not degraded even when the fin structure is introduced, and Renesas has verified that the same reliability characteristics as existing devices can be achieved.

The challenge when incorporating this fin structure SG-MONOS flash memory cell in a 16/14nm generation MCU is the increase in sample-to-sample variations associated with increasing the memory capacity. Renesas succeeded in overcoming this issue and verified its operation even in a large-scale memory, which marks a significant advancement towards the achievement of high-performance, high-reliability MCUs that include an embedded flash memory system in the 100MB class.

Renesas was able to demonstrate the following aspects of the large-scale embedded flash memory developed in this effort.

- Fabrication of a memory array using a fin-structure and confirmed large-scale memory operation

In fabricating this prototype, Renesas optimised the process conditions, including the deposition, etching, and ion implantation conditions, for the fin structure. As a result, Renesas was able to prototype a memory array without increasing the number of process steps and stably acquired, even at the array level, the short channel effect suppression and the effect of reduced sample-to-sample variations expected for from the fin structure. Therefore, Renesas targets to increase capacity to the large scales of over 100MB in a next-gen embedded flash memory. - Optimisation of the write method for fin structure memory arrays

Renesas announced last year that the step pulse write method (ISSP: incremental step pulse programming) in which the write voltage is increased in steps starting at a low voltage was effective in suppressing degradation of device characteristics caused by the enhancement of electric fields at the fin tips. Now, by using this method in array operation and optimising it, Renesas aimed at achieving both high-speed write operations and reliability. This contributed to achieving even faster write and erase operations than with earlier planar structures, and also confirmed almost no influence on write/erase speed even after the 250,000 rewrite cycles that was standard for earlier data storage flash memories. - Maintaining high-temperature data retention characteristics equivalent to existing devices at the array level

Data retention characteristics under high temperatures are critical for automotive applications. In this prototype, Renesas verified that the device maintains a guaranteed storage time after programming of at least ten years at 160°C, equivalent to earlier devices. Furthermore, this device maintains the sharp threshold voltage distribution that is a characteristic of the fin structure even after data is stored at the high temperature of 160°C at the array level, therefore maintaining the high reliability of existing devices.

The result represents a significant progress towards the achievement of high-performance MCUs that have four or more times the processing capacity of 28nm generation devices and that includes memory capacities in excess of 100MB for the 16/14nm generation and beyond, using SG-MONOS structure flash memory.

Currently, Renesas mass produces MCUs fabricated in a 40nm generation process using SG-MONOS structure flash memory and is also developing 28nm generation MCUs. Based on the demonstration of large-scale memory operation, Renesas plans to develop 16/14nm generation MCUs with a target of 2023 for practical applications and is committed to continuing to contribute to progress in the automotive field and the achievement of a smart society.