Flash with error correction supports the latest technologies

Can Flash with built-in error correction support the latest Flash technology without more complex 4-bit or 8-bit ECC? By Eugen Pfumfel, Principal Engineer, Memory Marketing, Toshiba Electronics Europe.

Driven by exploding demand from consumer and mobile markets, automotive and industrial sectors, and emerging IoT applications, Flash memory technology is moving aggressively to smaller and smaller process nodes. SLC NAND Flash, which stores one bit per cell and can endure around 60,000 write/erase cycles, is currently the most widely used Flash storage for these types of applications. The increase in Flash cell density achieved when moving from, say the 43nm process node to 24nm empowers end-product designers to enhance system functionality and offer greater user storage for content such as boot-image, operating-system image, programme- and application code within compact dimensions and at a competitive price.

One barrier to direct use of standard SLC NAND at smaller process nodes is that the smaller feature sizes mean individual cells are more vulnerable to stress-related damage. Over time the number of affected cells accumulates, resulting in an increased proportion of errors in the retrieved data. The only way to manage this gradual deterioration is to perform error correction on all data read from the device by executing an ECC algorithm.

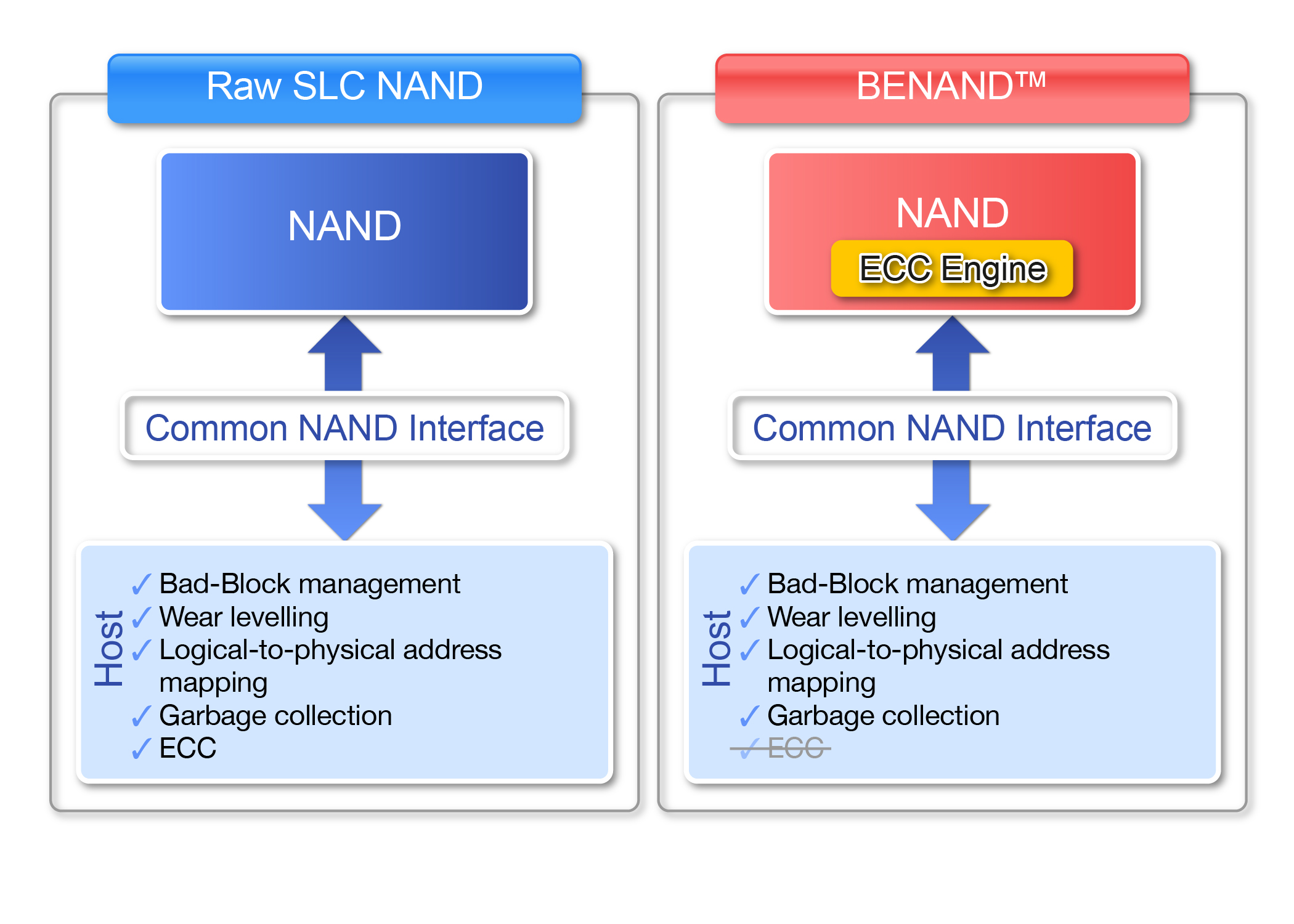

Figure 1 - Cost and ECC trends with advancing process technology

SLC NAND Flash fabricated at 43nm requires 1-bit ECC, for densities up to 4Gb. A 1-bit ECC algorithm is defined as being able to correct one failure bit per 512B. Increasingly complex error correction is needed at smaller process nodes; 4-bit ECC is required per 512B for sub-40nm SLC NAND, increasing to 8-bit ECC for devices fabricated at 24nm. Figure 1 illustrates how cost advantages are gained at the expense of increasing ECC complexity at more advanced process nodes.

When using raw SLC NAND, normal practice has been to execute ECC in the host processor. A 1-bit ECC algorithm has minimal impact on the overall processing budget for most applications. A 4- or 8-bit algorithm, on the other hand, demands a higher proportion of processor cycles, and may require a more powerful MCU leading to increased cost and power consumption. For an existing design the increased processor demand or the need for software changes may be prohibitive, thus preventing OEMs from updating to the latest-gen Flash.

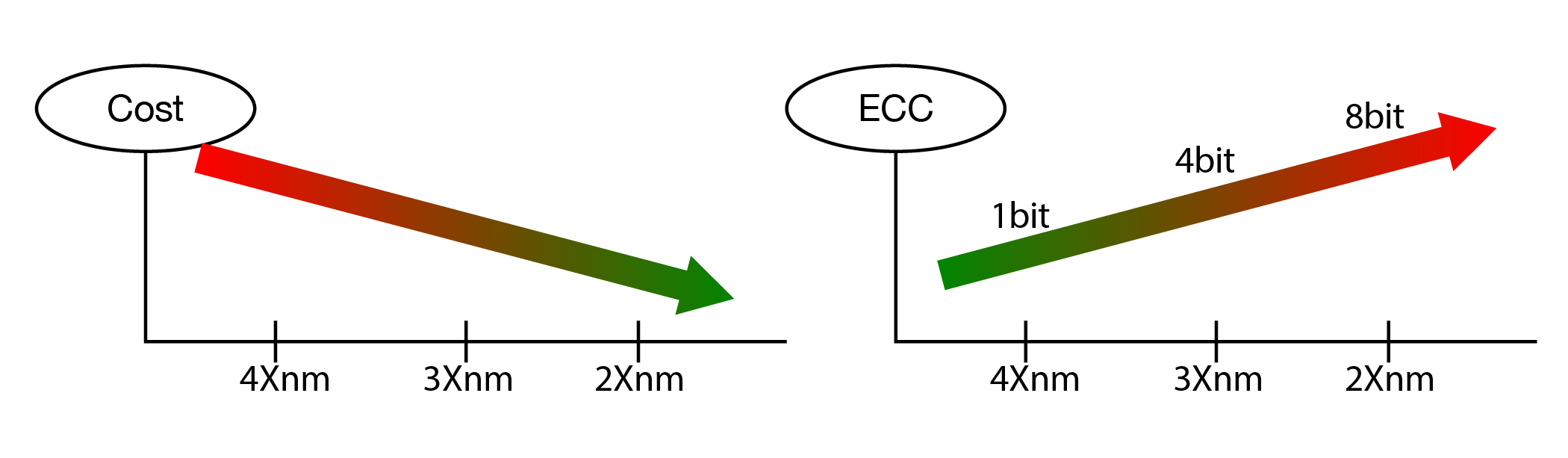

Built-in ECC NAND (BENAND) is a new type of SLC NAND Flash that has an embedded ECC function capable of offloading the burden of ECC from the host processor. No additional hardware controller is required, and BENAND uses the established and common NAND interface thereby ensuring compatibility with raw SLC NAND Flash in areas such as command set, device operation, packaging and pin configuration. The host system handles issues such as bad-block management, wear levelling, address mapping and garbage collection in the same way as with raw SLC NAND. Figure 2 compares the two approaches.

Figure 2 - BENAND offloads responsibility for ECC, and is compatible with the common NAND interface

The overall performance of BENAND is comparable or in some cases better than that of raw SLC NAND. Where the BENAND datasheet may state longer read and programme times, these are balanced by the absence of any host-side ECC processing.

Designing with BENAND

BENAND devices are available from 1 to 8Gb density, packaged as standard TSOP-I-48-P and 63-ball BGA devices that are pin compatible with known SLC packages. A tiny 6.5x8.0mm 67-ball BGA version is also available, which enables designers to meet tight space constraints in new designs.

Direct pin and package compatibility between raw SLC NAND and BENAND allows straightforward drop-in replacement when upgrading to the latest-gen Flash. Any existing host-side ECC is not required and should be disabled for optimum performance. If disabling the host-side ECC is not possible for any reason, the BENAND will in any case deliver ECC-corrected data to the host.

Since the BENAND takes full responsibility for ECC, and delivers valid data by correcting errors due to failed memory cells, the system is normally unaware of the physical condition of the NAND cells. If required, the system is able to check the ECC error status by executing a Status Read command. This outputs the number of error bits per data sector after a read operation, and allows the system to detect whether the data was either correctable, correctable but recommend to refresh, or not correctable.

Toshiba’s engineers have enabled a number of customers to integrate BENAND into existing or new designs, delivering the benefits of migrating to the latest device technology while helping avoid the high costs associated with significant system redesign or long-term use of legacy technology. For example, one customer achieved a cost-effective and satisfactory lifetime extension for a Bluetooth hands-free product aimed at the automotive aftermarket. The system architecture was built around a custom SoC combining an ARM processor core with ASIC functionality. The original design used SLC-NAND with 1-bit ECC to store the boot code, OS image, application code, application parameters and user data. The available processing budget was insufficient to meet the increased ECC demands of later SLC-NAND generations.

To ensure long-term viability, and so protect the OEM’s investment in the intellectual property inside the custom SoC, the OEM had considered a longevity support programme to guarantee supply of the original SLC-NAND components throughout the intended time in market. The cost of such a programme was successfully avoided by specifying a package-compatible 24nm BENAND device. This solution helped avoid any need to change the PCB design, while the more economical 24nm devices also delivered a cost-down benefit. Production was able to commence after brief system testing with the new BENAND devices.

Another customer was in the later stages of developing a small industrial control system combining an MCU with standard raw SLC-NAND, performing 1-bit ECC in the MCU, but foresaw problems arising from the introduction of later SLC-NAND generations fabricated at more advanced process nodes and therefore requiring more complex ECC. Since the application software was tightly linked with the peripheral features of the host MCU, changing the MCU for a higher performing variant capable of hosting up to 8-bit ECC would also necessitate significant software changes, adding extra cost and delay to the project. An alternative was, as in the previous example, to arrange a longevity support programme to ensure long-term supply of legacy SLC-NAND requiring 1-bit ECC. However, a 24nm BENAND device provided a more favourable solution.

As a direct drop-in replacement for the older raw SLC NAND, the BENAND delivers density and cost advantages, and is able to store all the boot code, low-level drivers for MCU peripherals, OS image, application code, application parameters, and user data, as before. Migrating to the later technology also provides the assurance of long-term supply without requiring a dedicated support programme. As before, the project was able to progress after brief system testing with the BENAND devices fitted.

As designers face unrelenting pressure to deliver greater functionality at increasingly competitive prices are compelled to use the latest memory technologies, such as 24nm SLC NAND Flash. Long-term use of older technology carries supply risk and imposes extra expense. BENAND Flash with embedded error correction simplifies migration of existing and new designs, offering speed, flexibility and cost-effectiveness as a direct replacement that imposes no additional software overhead on the host system.