The RISC-V open-source extensible ISA gathers momentum

New instruction set architectures don't come about very often in the semiconductor processor industry. The last significant change saw Arm develop cores and sell them as an IP license, in an instant changing how leading vendors of that era go about designing processors. Now, in a time of trade-wars and a pandemic, the availability of an open-source, royalty-free, extensible ISA is proving to be a transformative and disruptive force.

By Mark Patrick, Mouser Electronics

The processor ISA has changed little in 40 years

For decades Intel and Arm have dominated the processor architecture landscape. Intel and its x86 architecture own the computer workstation, desktop, and server space. Meanwhile, Arm has established a broader marketplace from IoT devices, consumer electronics, and industrial automation systems.

Other embedded processor and microcontroller architectures, such as Atmel's AVR and Microchip's PIC/MIPS, have found their niche but have not achieved the dominant players' critical mass. Arm's IP licensing model has been widely adopted by most MCU and MPU vendors within the embedded systems environment. However, a disruptive, transformational change is rapidly gaining momentum and starting to challenge the processor market's norms.

Leading vendors are quickly adopting the open-source, RISC-V instruction set architecture (ISA) as customers embrace the commercial and technology benefits that an open-source approach brings. In this article, we document the birth of RISC-V and highlight some of the factors that make it attractive. We include product examples, focus on evaluation boards, development resources, and the growing ecosystem of software toolchains.

ISA – the real link between processor hardware and software

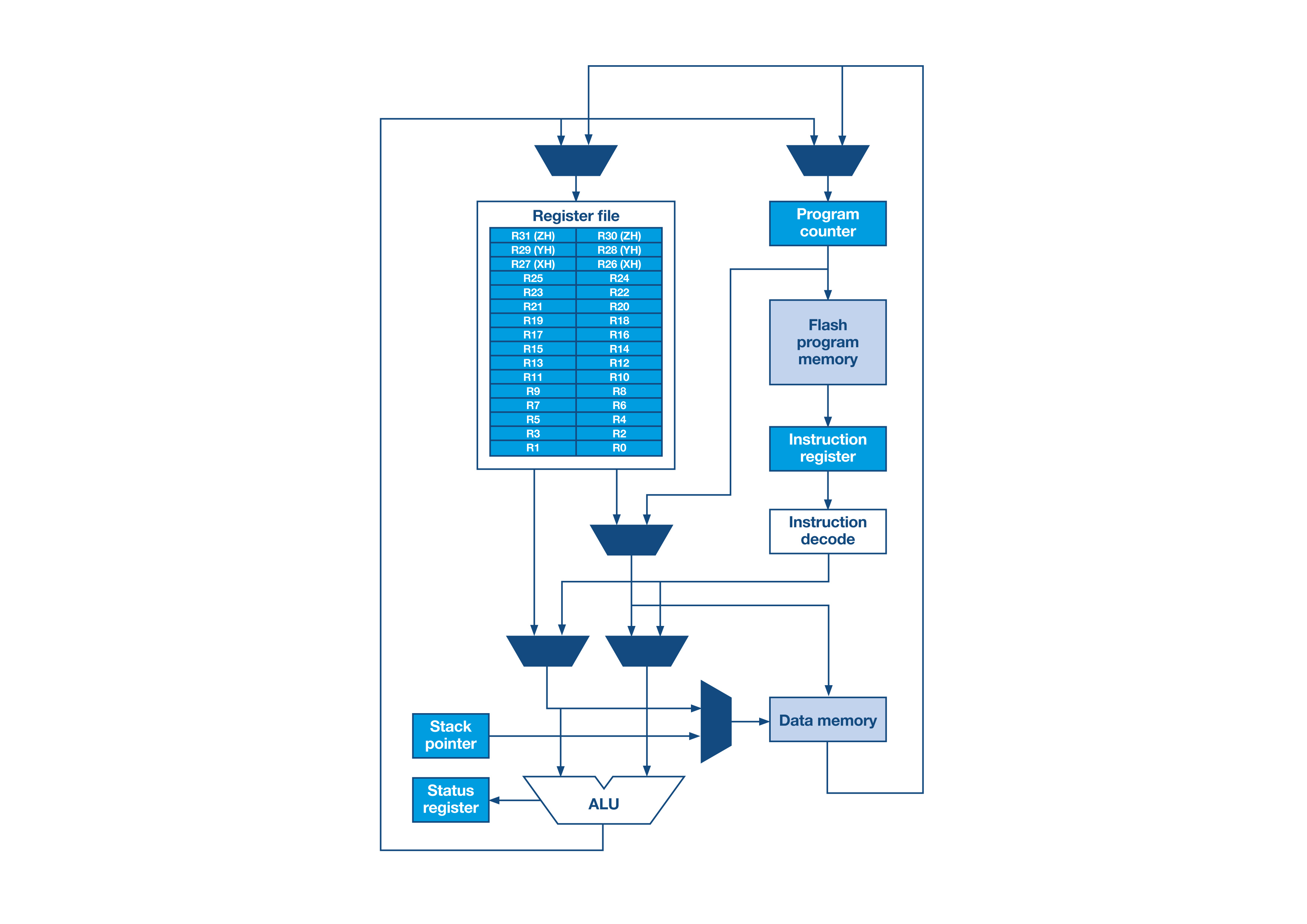

An instruction set architecture (ISA) provides the interface between the worlds of software and a processor's hardware. The ISA defines every aspect of how a program interacts with the available hardware, including the arithmetic logic unit (ALU), registers, memory, and control logic. It also specifies the word length, the supported data types, and how registers and memory locations are addressed. In short, an ISA is an abstract of a processor.

There are many different ISA types, but for most practical purposes, the two most important types are complex instruction set computer (CISC) and reduced instruction set computer (RISC). As the name suggests, a CISC contains many complex and specialised instructions for various applications, some of which might feature rarely. A CISC processor also features many different addressing methods and uses instructions of variable lengths. CISC-based processors are expensive to design, require more sophisticated software and programming tools, and take significantly longer to design. An example of a CISC ISA is the Intel x86.

By contrast, a RISC-based processor is much simpler and has a limited set of frequently used instructions, a few different addressing modes, and a fixed instruction size. The use of instruction pipelining techniques permits faster execution throughput. Unlike a CISC processor that moves operands (data values) out to memory to perform calculations, a RISC processor uses internal registers. Examples of a RISC-based ISA include Arm, AVR, PIC, and MIPS.

Figure 1: Example of a Microchip AVR microcontroller RISC architecture.

ISAs – what are the critical success factors?

For the rest of this article, we'll concern ourselves with only RISC-based processors. When referring to a processor, the context refers to any processing device, such as microcontrollers and microprocessors. Popular RISC ISAs are available with 8-, 16-, and 32-bit word lengths, with 64-bit and 128-bit ISAs typically used for more demanding and specialist applications. The word length has a significant impact on the hardware design, the speed the processor can operate, and the available memory size.

As a minimum, an ISA needs to include an arithmetic logic unit, memory, and control logic. The ALU performs basic arithmetic computational functions such as adding, comparing, and subtracting, using registers or in an 'immediate' manner within itself. Memory addressing can be absolute or indexed. Control logic performs conditional and unconditional branching and other addressing tasks.

The instruction set of an ISA consists of opcodes (machine code) that specify the task to be performed, usually on an operand(s). For example, within the Atmel/Microchip AVR ISA, ADC defines adding together operands held in two registers with a carry flag and places the result in the destination register. The ISA documentation will indicate how many clock cycles or program counter iterations each instruction will take. In a RISC processor, the majority of instructions will be single-cycle.

For microcontroller (MCU) and microprocessor (MPU) vendors, developing an ISA is a core component of designing their products. In this way, ISAs have become proprietary, created for a specific series of devices. Examples include the Atmel/Microchip AVR (8, 16, 32-bit), the Microchip PIC (8, 16, 32-bit), and MIPS (32, 64-bit).

Advanced RISC Machines (Arm) broke the traditional MCU/MPU business model in the early 1990s when the company formed as a spinoff from Acorn. Arm's approach took the IP licensing route, creating its revenue stream from royalty payments rather than fabricating and selling devices. Arm's model quickly took off, freeing semiconductor vendors of the task of developing and porting their ISA.

Today, most semiconductor vendors provide processors based on the Arm ISA, and some also supply devices based on their ISA. Each pays a royalty to Arm for each device sold. Arm controls the lifecycle and on-going development of the ISA.

While individual ISAs have their pros and cons, the success of any particular processor architecture depends not only on its technical merits but on the availability of an ecosystem of software development tools. Toolchains, integrated development environments, compilers, debuggers, and application-specific middleware have a vital role in growing the popularity of a processor and it’s ISA.

Open-sourcing the instruction set architecture

For semiconductor vendors, Arm brought about a standard ISA around which they could adapt and enhance the device's peripheral interface options to suit specific applications. This approach has facilitated a degree of product differentiation against other semiconductor competitors also using Arm IP. To the established ISAs such as AVR, PIC, etc., the widespread adoption of Arm has reduced their overall reach into the market.

However, for processor customers, making an architectural decision to adopt an Arm ISA is prudent since there are multiple processor vendors, thus facilitating a choice of purchasing options for second sourcing of similar parts. Standardising development around a specific toolchain also makes commercial sense.

In an industry that has embraced many open-source concepts, the processor instruction set architectures' domain looked very proprietary. That is until the RISC-V ISA appeared in 2010. Initially developed at the University of California, Berkeley, as an ISA for academic purposes, the concept of developing making the ISA open-source took hold rapidly.

The rationale for it being open-source came from the thought that ISA design had changed little in the past forty years. Making it open would encourage more interaction and software reuse, hopefully attracting long-term support from vendors' toolchain suppliers. As an open-source ISA, vendors do not have to pay any royalties and are permitted to make new instructions and extensions.

The base RISC-V ISA and associated extensions are developed and managed as a collective effort between the academic research community and industry. RISC-V ISA supports 32-, 64-, and 128-bit word lengths.

In 2015, RISC-V development took a significant step forward when a collaboration of semiconductor companies founded the RISC-V Foundation. The appeal of paying no royalties and extensibility proved to capture vendor attention. Arm licensees cannot tweak the instruction set to suit specific applications - low power, for example, but RISC-V licensees can. The RISC-V Foundation has over 750 industry members.

As many major processor vendors started to show interest in RISC-V, the software tools community, not wanting to be left behind, began to extend support for RISC-V in their IDEs and toolchains.

Getting started With RISC-V

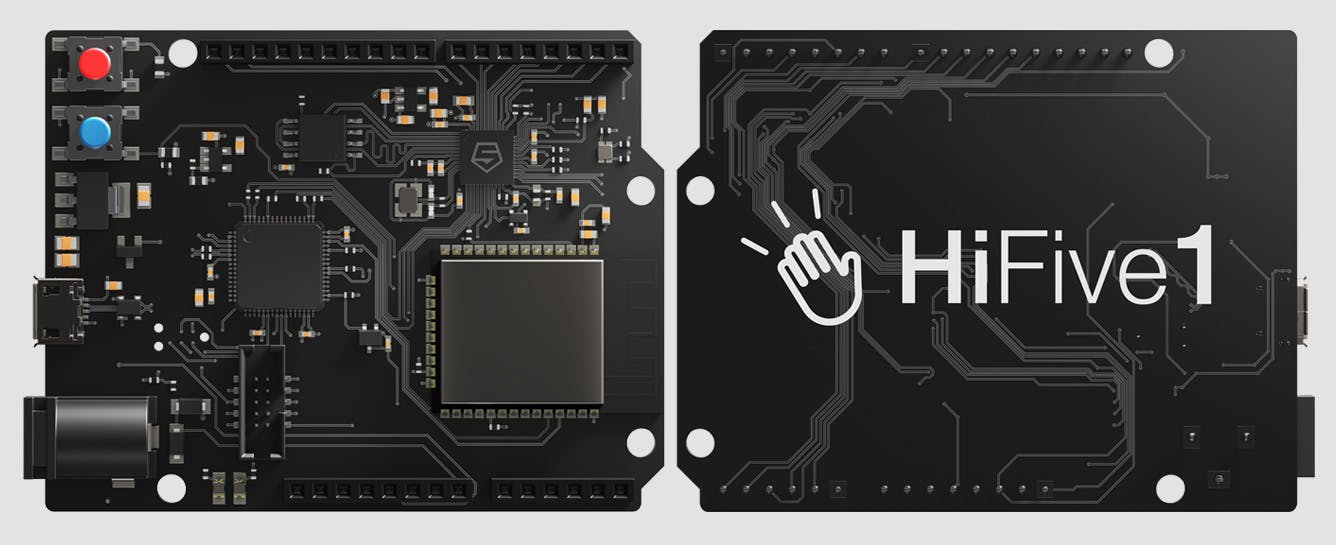

One of the first RISC-V-based 32-bit processors available was the SiFive Freedom E31 SoC. SiFive was established by the RISC-V ISA founders and quickly looked to bring their expertise to the market. To encourage prototyping SiFive crowdfunded a low-cost Arduino form-factor development board, the HiFive1. The SiFive HiFive1 B incorporates Wi-Fi connectivity and 32 Mb of flash memory.

Figure 2: The SiFive HiFive1 B development board.

SEEED also supply a Feather/MKR-format development board, the Sipeed Longan Nano – equipped with a 0.96 inch LCD, uses a GigaDevice 32-bit RISC-V core.

SparkFun supplies a development board similar to HiFive1 B. The SparkFun RED-V RedBoard also uses the Arduino UNO-R3 form-factor and the SiFive E310 RISC-V SoC.

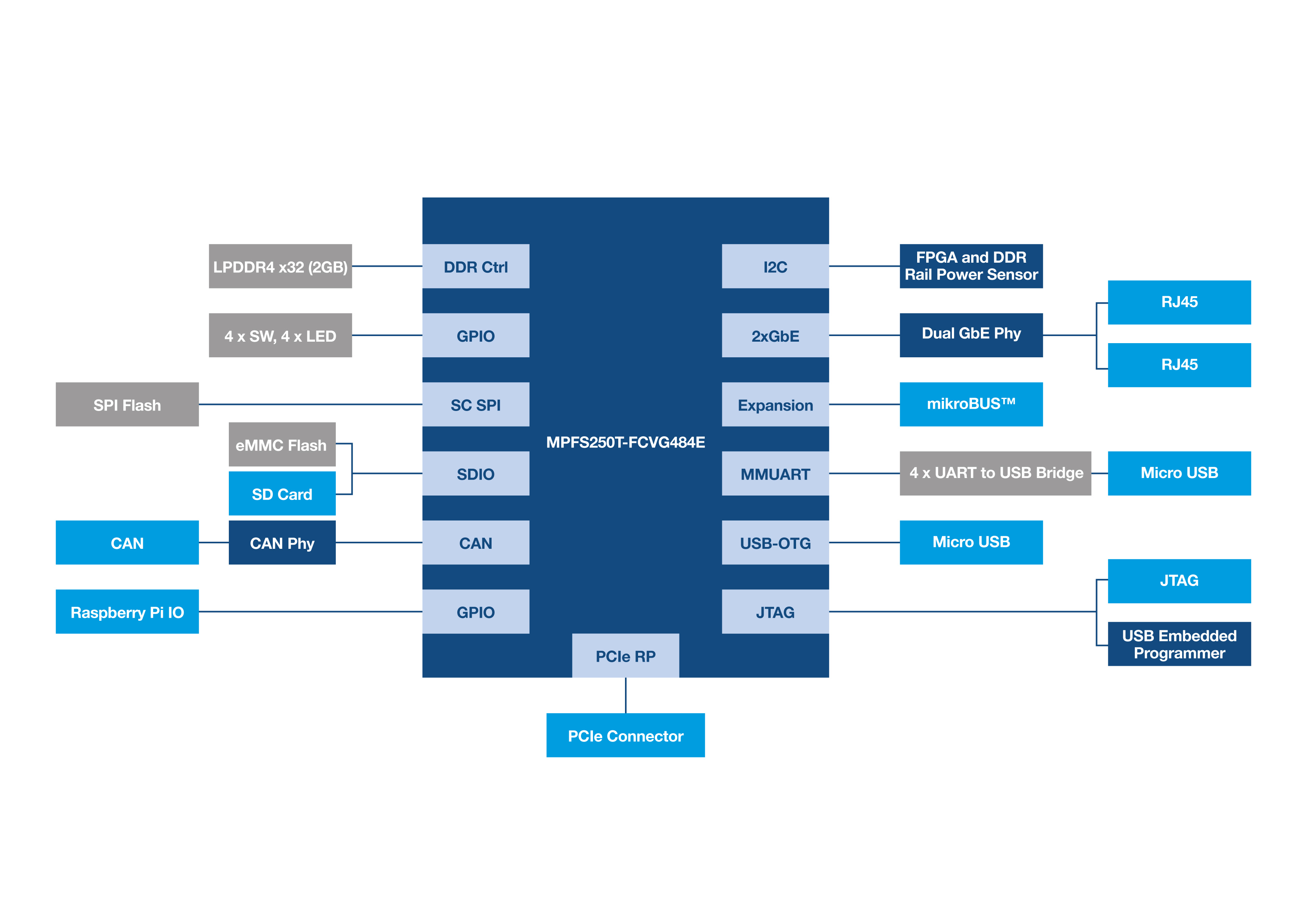

A more comprehensive RISC-V platform aimed at the professional engineer is the Microchip PolarFire SoC FPGA Icicle development board.

Designed to provide an evaluation platform for the five-core, Linux capable RISC-V RV64 core, the PolarFire SoC is also equipped with 256k logic elements and a 784 element math block. Well suited for prototyping real-time, low power designs, from IoT sensors to machine learning applications, the Icicle kit includes comprehensive peripheral interface connectivity, including HDMI, PCIe, USB, CAN, SPI, and I2C. External expansion interface options include a mikroBUS socket and a Raspberry Pi 40-pin connector.

Figure 3: Functional block diagram of the Microchip RISC-V PolarFire SoC evaluation kit.

RISC-V: the journey ahead

In a relatively short period, the RISC-V instruction set architecture has gathered significant momentum. The Foundation celebrated the tenth anniversary of the initial RISC-V development during July 2020. According to the Foundation's website, there are now 12 RISC-V-based SoCs commercially available and 86 cores.

RISC-V has quickly established itself as a viable extensible, and royalty-free alternative to other ISAs.