Pervasive connectivity is changing the FPGA landscape

The emergence of pervasive connectivity - and the resultant volumes of data that creates - could be changing the landscape for embedded electronics, meaning the old mandate of ‘faster, smaller, cheaper’ may soon just read ‘faster’. Philip Ling, Editor, ES Design magazine, reports.

For many years, embedded electronics has enjoyed its position in the modern world as an enabling technology; it not only led the way, it set the pace. Now, it seems, the modern world has had enough of following and, instead, wants to be the driving force. Of course, semiconductor vendors have always had to strive to meet market demand but in most cases that demand was created by those same companies. Now the wider world has a better understanding of what’s achievable, it looks like demand could be outpacing technology.

Or at least it would, if those same semiconductor vendors weren’t willing to embrace change and adapt to the prevailing conditions. One technology that offers more flexibility than most in this regard - and is its real modus operandi, in fact - is configurable logic in the form of CPLDs and FPGAs. It is invariably at the forefront of manufacturing process nodes and strives to deliver more performance with every generation, without compromising on flexibility. However, it seems that may be open to interpretation with the latest wave of product offerings.

The harder the better?

The use of hard IP in an FPGA fabric started around two decades ago and initial attempts to provide hardened processors within a sea of gates had moderate success. But in the last two to three years, the two market leaders - Xilinx and Altera - have really tapped in to the potential, by adopting the ARM Cortex architecture. With that lesson learnt, it looks like Altera is prepared to go even further and embrace hard IP to deliver greater DSP performance, too. This is an interesting move, because the FGPA fabric is often touted as being the most optimal way of implementing digital signal processing functions, thanks to its ability to provide massive parallelism. Altera claims it makes it the first programmable logic company to integrate hardened IEEE 754-compliant floating-point operators in an FPGA, stating that it will allow its devices to address an expanding range of computationally intensive applications such as high-performance computing and imaging.

By implementing the DSP blocks as hardened IP, rather than fixed-point multipliers and logic, eliminates the need for logic; a game changing innovation according to Altera, which delivers up to 1.5 TeraFLOPs DSP performance in Arria 10 devices and up to 10 TeraFLOPs in Stratix 10 parts.

“The implementation of IEEE 754-compliant floating-point DSP blocks in our devices is truly a game changer for FPGAs,” said Alex Gabric, Director of Software, IP and DSP Marketing, Altera. “With hardened floating point, Altera FPGAs and SOCs offer a performance and power efficiency advantage over microprocessors and GPUs in an expanding range of applications.”

Companion device

Despite the demand for performance, manufacturers still recognise the benefits FPGAs can bring to design in terms of configurability. Indeed, their flexibility is in such high demand that some vendors, specifically Lattice Semiconductor, are going to great lengths to pare down the FPGA to offer the barest of functionality. Its latest family, the ECP5, is focused on applications that require less than 100k Look-Up Tables (LUTs), to provide critical functionality in the smallest possible footprint.

“The ECP5 family breaks the rule that FPGAs should be the highest density, power hung and expensive,” said Darin Billerbeck, President and CEO, Lattice Semiconductor. “Lattice’s newest family serves to provide customers with an ASIC/ASSP companion chip as the quickest path for removing development obstacles at a a time when mobility and mobile infrastructure are driving the need for small size and low power in practically every facet of the electronics industry.”

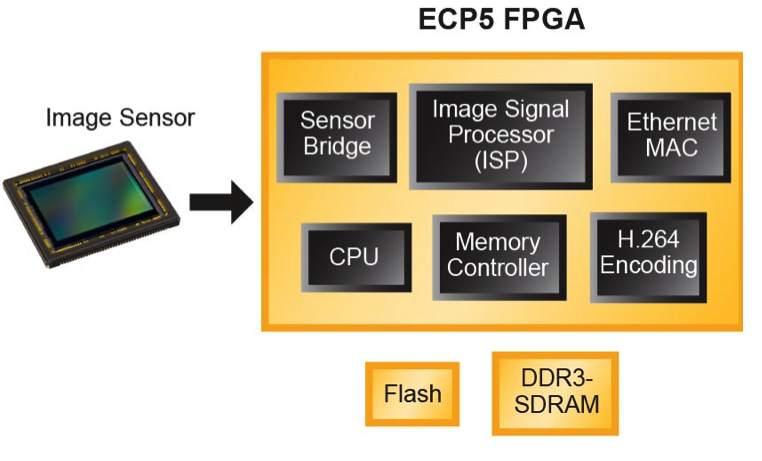

Figure 1 - Fitting the entire image processing functionality of an industrial video camera in to just 100k LUTs

Lattice believes size is key in the applications it is targeting with the ECP5, which includes emerging markets for small cells and micro-servers, as well as surveillance cameras. In these applications, large FPGAs consume too many resources (power, space) and so ASICs and ASSPs remain dominant. The problem comes when the manufacture needs to extend functionality - typically in terms of connectivity, something ASICs/ASSPs struggle to accommodate. As Figure 1 shows, even 100k LUTs can offer a great deal of extensibility in this regard; Lattice claims that an ECP5 can implement the entire image processing functionality of an industrial video camera in a device that consumes less than 2W.

The interesting aspect behind both these introductions is that the traditional benefits of an FPGA are being ‘downplayed’ somewhat, bucking the established trends in order to better address the market’s needs. In the end, that’s something programmable logic really should be well placed to deliver.