Microcontrollers and peripherals take centre stage

Some of the programme highlights from the upcoming Embedded Platforms Conference at electronica 2016 include expert technical presentations on NAND Flash reliability, core independent MCU peripherals and speedy development of embedded software. Sally Ward-Foxton investigates.

Day one of electronica 2016 will see the Embedded Platforms Conference kick-off with an IoT and security theme and a microcontrollers and peripherals track taking place side by side. Here’s a preview of some of the highlights of the microcontrollers and peripherals presentations scheduled for the show.

High reliability NAND Flash

Toshiba’s Flash memory expert Eugen Pfumfel will present a paper on how to avoid faults when using embedded NAND Flash in high reliability systems. Developing for applications like industrial electronics, which demand the highest levels of reliability in challenging environments, can be difficult when working with embedded memory sub-systems. Pfumfel’s presentation will reveal some helpful design tips for getting the highest possible reliability out of NAND Flash technology.

To start with, there are many different NAND Flash technologies on the market, but some are more reliable than others, Pfumfel explained: “In general, SLC (single layer cell) NAND technology delivers the most reliable NAND products, while MLC (multi-layer cell) and TLC (triple layer cell) NAND address requirements for higher program/erase cycles,” he said. “Toshiba produces SLC NAND in 43nm, 32nm and 24nm to meet customers’ demands for high reliability. We use a special software algorithm to increase reliability, handling things like wear levelling, which ensures all cells are used equally. These technologies are widely used in embedded systems and industrial cards.”

Where the application demands high density, low cost memory, managed NAND solutions such as eMMC (embedded multi-media card) may be used. While eMMC has lower program/erase cycles than SLC NAND because it uses MLC (or in a few cases, TLC), reliability can be increased by switching the initial configuration from standard mode (MLC) to high reliability mode, which is effectively pseudo-SLC operation.

Pfumfel explained that while no NAND Flash technology has an endless data retention time or unlimited number of program/erase cycles, there are a number of design techniques that can be used to increase reliability by avoiding memory errors as far as possible. There are two types of NAND errors to consider - hard errors and soft errors.

“Hard errors happen during program and erase, where the NAND cell structure becomes damaged at the end of its life. ECC [error correction code] can help, but in the end there will be a bad block,” he said. “Soft errors can happen as a result of high temperature and if cells are influenced by the activities of neighbouring cells, for example, in a read operation where address/word lines are toggling. Such errors do not damage the NAND cell structure and a cell override can re-configure the old cell load (the electrons).”

Another tip from Pfumfel is for designers to be aware of the read/write usage model of their applications. For example, a boot image is only programmed once and should stay stable over the product’s lifetime. An OS image might be written rarely during product lifetime, while program/application images may be written regularly. Frequently written images should be in a separate partition to guarantee the longest possible data-retention time, while other frequently written data like log files should be buffered, if possible.

“To avoid frequent block erases, which mostly request the copying of used pages from the target block to be erased, over-provisioning may help,” Pfumfel added. “The used page copies created before block erase represent garbage collection, and result in a write amplification factor where an image written by the host ends in frequent copy routines.”

Core-independent peripherals

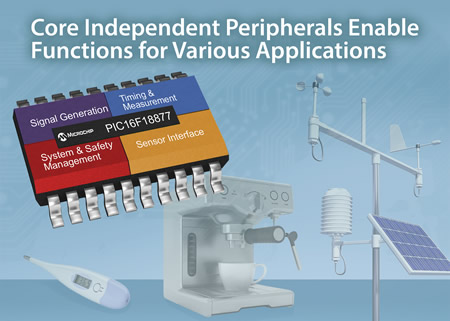

Microchip’s presentation at the conference will be about its core independent peripherals (CIPs) - digital microcontroller peripherals that are completely self-sufficient, eliminating the need for the CPU to handle all of the events, which would otherwise be a performance bottleneck.

“(CIPs) provide fast reactions to external events, allowing a humble 8-bit microcontroller to provide a solution that would otherwise require the cost, complexity and power consumption of a DSP,” said Lucio di Jasio, EMEA Business Development Team Leader at Microchip. “CIPs are used with great effect in illumination, motor control, medical applications, touch sensing and capacitive sensors in general, distance measurement, signage, small appliances, access control and remote control - and that’s mentioning only a few recent cases.”

Though the field of potential applications is very broad, Microchip’s presentation will focus on using CIPs in power supply designs. “Between the traditional, relatively well understood by most, analogue power supply solutions and the most advanced, complex DSP/digital power solutions there is a vast gap, and the CIPs can help bridge it,” he added. “The application of the CIPs and our design philosophy can bring simplicity while providing a superior solution, compared to the traditional analogue approach.”

Above: Microchip’s PIC16F18877 family features CIPs that enable functions in a broad range of applications, such as consumer electronics, IoT and safety critical systems

The paper will detail a hybrid approach, taking advantage of the integration of analogue peripherals already on the same microcontroller chip, and a flexible analogue internal connection network. And freeing the CPU from handling all external events means it can be downgraded from a DSP to a smaller, cheaper microcontroller.

Another benefit di Jasio cites is that the code required to configure the CIPs is relatively straightforward (the CIPs are only configured during power-up in the power supply example, but they can be reconfigured during use if required by the application).

“In traditional applications, a significant amount of complex code is required to handle the continuous stream of interrupts coming from the traditional peripherals. Timing of this code can be critical and its size is often directly correlated to the testing and validation time of the application,” he added. “With the CIPs, that code is reduced, if not completely removed, resulting in a size reduction but much more importantly in a complexity reduction that is often reflected in significant testing and validation cost savings.”

With CIPs, since the microcontroller core is not interrupted as often, if at all, the clock frequency requirements are often reduced considerably, in direct contrast to traditional designs where interrupt response latency is a big concern. A bonus side-effect is that there is a proportional power consumption reduction with the smaller microcontroller chosen.

Embedded software in 15 minutes

Renesas’ Kimberly Dinsmore will also present at the Embedded Platforms Conference. Her paper is entitled ‘Create an Embedded Software Application in 15 Minutes’, and it will detail the use of software frameworks and configurators to get embedded applications to market as quickly as possible. Dinsmore points out that to remain competitive, today’s products need to include complex components such as colour LCDs, touch control interfaces, and wireless connectivity as standard, while time to market is under continually increasing pressure.

“Individually, all of these technologies are complicated, but the true challenge is enabling them to interact with each other,” she said. “Resource sharing, managing processor bandwidth, as well as basic data and process flow must all be taken into consideration. A comprehensive platform with flexible frameworks, aided by an IDE with intuitive graphical configurators, can solve these puzzles, and make the difference between being a market leader and a market follower.”

Other presentations

The Embedded Platforms Conference microcontroller and peripheral track at electronica 2016 will take place on 9th November. The other presentations scheduled in this track are:

• ‘Arduino look and feel for multicore’ by MicroConsult’s Marcus Goessler.

• Jacko Wilbrink from Atmel with ‘Hit your application sweet spot with the right Coretex-M7 MCU’.

• ‘Efficient embedded programming of heterogeneous multicore platforms’ by Dr. Timo Stripf from Emmtrix Technologies.

• Analog Devices’ Tom Meany will discuss what functional safety module designers need from IC developers.

• Jeffray Hsieh from ATP will speak about optimising SSDs for enhanced performance.