SFN's ‘Infrastructure Time Machine’ for chip designs

Search for the Next (SFN) has made available a family of four ITMs (Infrastructure Time Machines) – which can be considered process nodes – that enable chip designers to produce ICs in older 180nm and even one-micron geometry fabs with the equivalent performance of CMOS devices made in current state-of-the-art plants.

As an example of the above, a fab equipped with 180nm photolithographic steppers – such as Newport Wafer Fab, the UK’s largest semiconductor production plant which is at the centre of a political and trade war over its proposed sale to foreign owners – could now produce ZTL devices with the performance (size, speed and performance) of 35nm CMOS by implementing ITM35...and at a hugely reduced cost.

Explains David Summerland, CEO of SFN: “Until Bizen, the Zpolar transistor and ZTL logic, high performance chips for applications such as 5G and RISC-V could only be produced at facilities such as the Taiwanese giant, TSMC, which controls most of the world’s high-performance semiconductor production. Now, UK and other Western fabs can be competitive again, and even overtake the Taiwanese and Korean giants, while also securing best national interests and IP.”

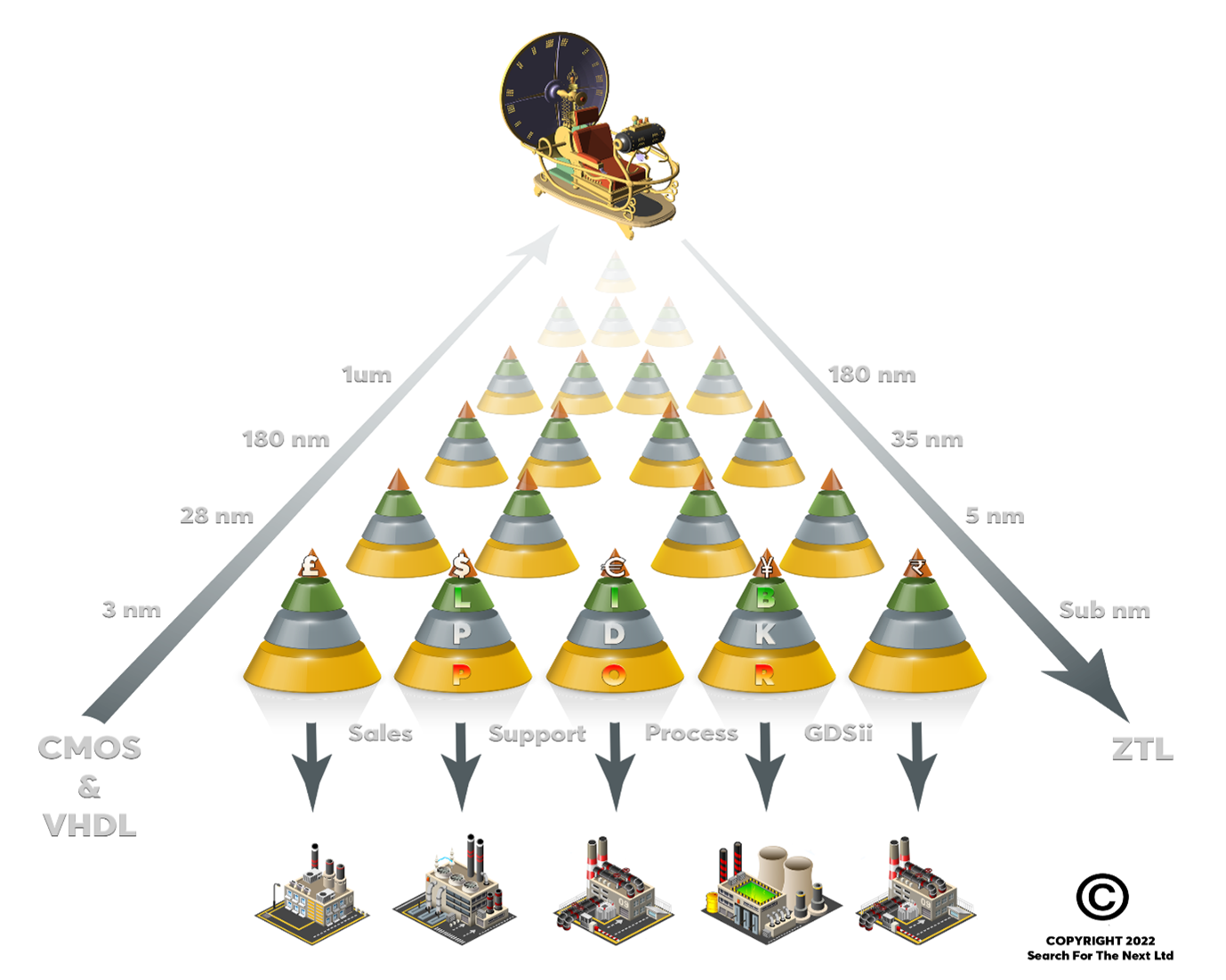

SFN is releasing four ITMs: ITM180 which can deliver ZTL chips with the performance of 180nm CMOS using one micron equipment; ITM35 which enables 35nm CMOS-equivalent ICs to be made in 180nm process node fabs; ITM5 which enables 5nm CMOS performance from 28nm steppers, and ITMSubnm which means that current state-of-the-art 3nm fabs will be able to deliver incredible sub-nm, Angstrom-level capabilities. VHDL is taken into the chosen ITM, which delivers both the POR (process of reference) and the GDSii for the resultant IC to the fabs. The Infographic shows this process.

Infographic: The Bizen Infrastructure Time Machine (ITM)

On the left axis we see CMOS fabrication nodes stretching back in time from today’s 3nm state-of-the-art. Each row represents approximately one decade. The right axis shows the CMOS node that would be required to achieve the performance that the compound combination of the Bizen wafer process Zpolar transistor and Zpolar Tunnel Logic (ZTL) can offer. The increasing number of cones shows how markets have widened each decade from just the computers applications of 60 years ago, to today, where the micro chip is ubiquitous and used in everything from the IoT, EVs, communications and consumer goods through to defence and other nationally-strategic and sensitive installations.

Foundries can use the ITM process nodes to employ an older CMOS-equivalent processing node to produce ZTL-based chips which offer orders-of-magnitude performance increases over their now-obsolete CMOS equivalents. VHDL is taken into the selected ITM (dependant on performance requirements) from chip designers. The ITM, which contains the fully-characterized device libraries (LIB) and Process Development Kit (PDK), supplies both the Process of Reference (POR) and GDSii information to the foundries to make the ZTL chip.

Bizen applies quantum mechanics to any wafer process technology. Bizen ZTL chips require far fewer processing layers, enabling complex devices to be manufactured in large-geometry fabs around the world. Details Summerland: “A 180nm fab using ITM35 delivering ZTL chips with the equivalent performance of 35nm CMOS will have ten times fewer process steps than an actual 35nm CMOS process, resulting in a 10 fold reduction in production time. This translates into a 40-50 fold increase in net profit for the Bizen-converted fab. At the same time, this massively contributes to solving semiconductor shortages.”

Although a new technology, the Bizen process can run on standard silicon process technologies using standard CMOS processing equipment. Bizen has been in development at a UK fab for four years, and SFN has produced ‘gold standard’ test wafers, which have been characterized. The extracted characterization data has been put into a JMP data book and used to produce SPICE models which run in the Cadence design environment, and matches the results from the Synopsis wafer process flow.

Concludes Summerland: “We are aware of CMOS technology roads stretching out to at least 2036 with device geometries down to two angstroms. It is important to understand CMOS is logic, MOS a transistor. Even CFETS are stacked nMOS and pMOS. Bizen/ZTL is a huge step forward and will render other complex approaches redundant. Zpolar transistors move away from a reliance on the unipolar structure of CMOS, to take advantage of an inherent hair trigger input and minimised vertical size.

"We believe ‘Time Machine’ is the best description for the compound combination of the Bizen wafer process, Zpolar transistor and Zpolar Tunnel Logic (ZTL): using this technology, IC designers can go back 10 years in manufacturing capabilities, then forward 10 years – or more – in performance terms, with the ZTL devices they create. Since the ICs are so much simpler to produce, and/or more chips can be made per wafer, we are also solving the semiconductor shortage crisis, and at the same time, eliminating our reliance on foreign powers and their roads. Where we're going, we don't need roads.”