IP subsystem for implementing 10 Gigabit Ethernet

In partnership with MoreThanIP, a provider of telecom solutions, Toshiba Semiconductor & Storage Products Company, has developed an IP subsystem designed to easily implement a 10 Gigabit Ethernet interface subsystem into a system LSI.

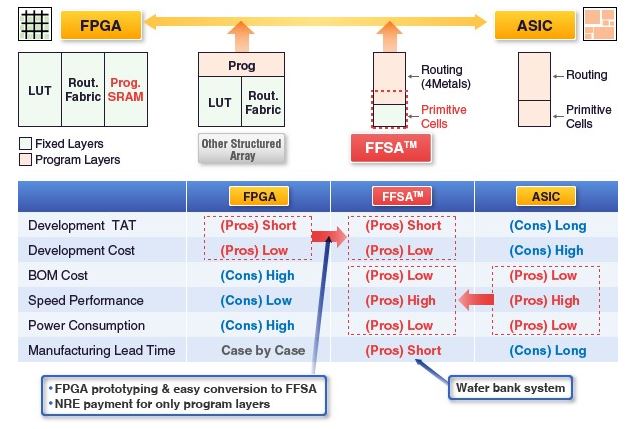

The IP subsystem consists of a 10 Gigabit Ethernet MAC (media access controller), PCS (physical coding sub-layer) and high speed SerDes (Serialiser Deserialiser) for custom LSI platforms, including ASIC and Toshiba’s FFSA.

The sub-system implements a 4-lane XAUI or a single Lane XFI interface that provides connectivity to a large number of Ethernet PHYs and controller ASSPs (Application Specific Standard Products). With support for PFC (Priority Flow Control) and a high level of flexibility, the IP subsystem is well suited for data centres and telecoms applications.

“Together with Toshiba’s custom LSI solutions and MoreThanIP proven cores, chip producers will now have an integrated solution at their disposal to help speed the design cycle and meet the needs of the growing high speed Ethernet market,” said Francois Balay, CEO of MoreThanIP.

“Collaboration with MoreThanIP allows us to propose an integrated Ethernet offering with best in class IP cores for custom LSI solutions,” said Yukihiro Urakawa, Technical Executive of Toshiba.

FFSA is a new, flexible custom LSI solution with pre-designed masters featuring configurable I/Os, SerDes, SRAMs and logic devices that can be configured according to customer requirements.