When will 3D TSV be used for mainstream consumer applications?

Yole Développement has released a new report '3DIC & 2.5D TSV Interconnect for Advanced Packaging - 2014 Business Update' which provides an overview of the TSV implementation for various devices and packages including memories, logic, MEMS, photonics, CIS and other applications.

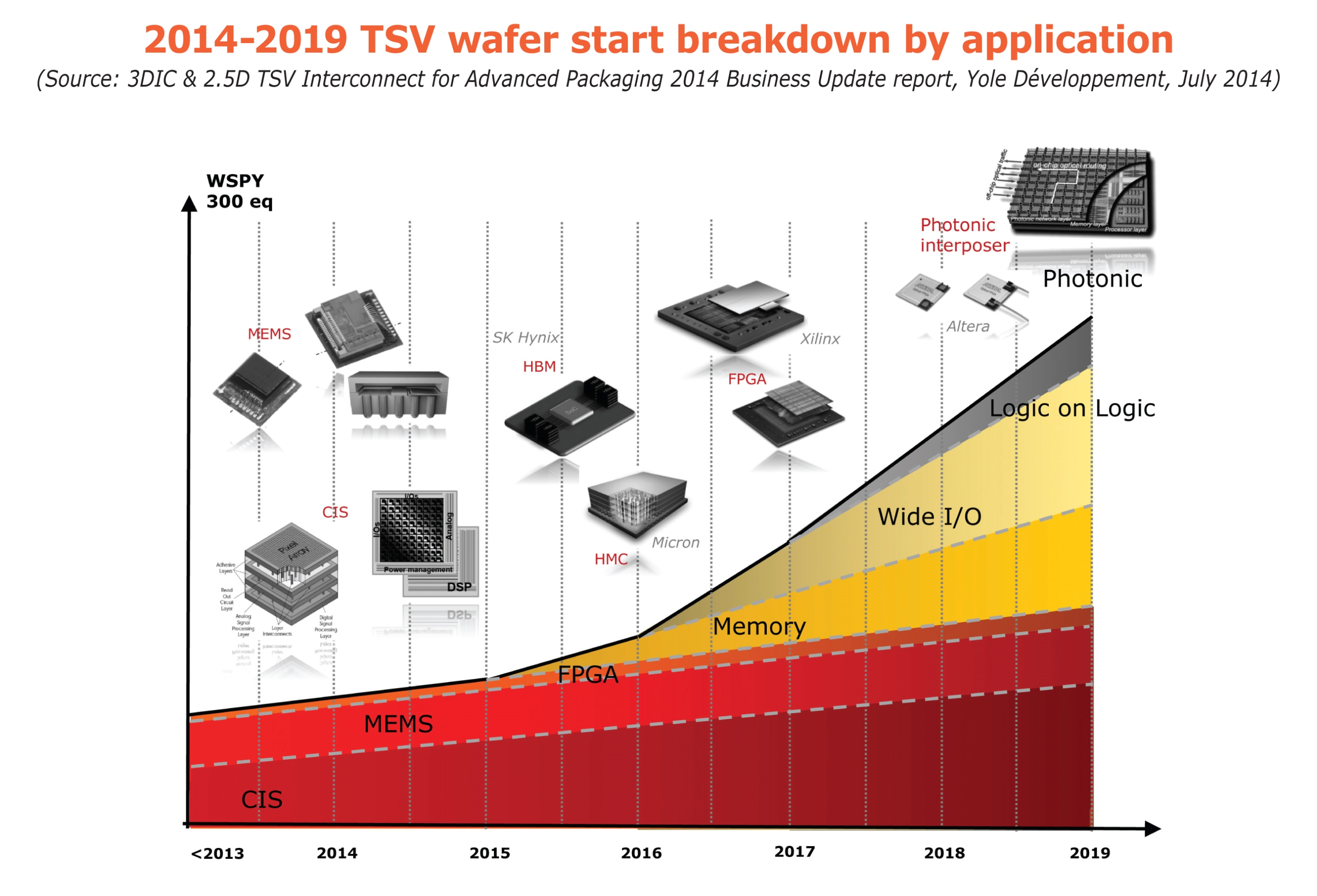

While currently used for MEMS, CMOS Image Sensors and high-end applications, when will 3D TSV (Through Silicon Vias) be used for mainstream consumer applications? The report analyses future 3D products for high-end applications and alternative packaging technologies (fan-out, advanced organic substrates, monolithic 3D). Yole also details the market adoption roadmap and wafer start by platform and by application.

Thibault Buisson, Technology and Market Analyst, Advanced Packaging, Yole Développement, comments: "Driven by consumer applications such as smartphones and tablets, this market is expected to continue to grow over the next several years. For high end memories, 2015 will be the turning point for 3D adoption. Standards have now been established, therefore the industry will be ready to enter in high-volume manufacturing. Wide I/Os and logic-on-logic will follow, most probably around 2016-2017. Emerging applications, such as photonics based on interposer, are also being developed for future products. However, their market entrance is most likely not going to happen before 2019-2020.”

Yole believe that the market drivers have not fundamentally changed over the years. 3DIC is still driven by the need to increase performance and functionality, and to reduce form factor and cost. Adoption of 3DIC technology is being considered for a wide range of applications - due to its many advantages including the ability to enable heterogeneous integration.

“There is a significant advantage to using 3DIC and that is why this packaging platform is part of all the roadmaps of the key semiconductor players across the entire supply chain," adds Rozalia Beica, CTO and Business Unit Director, Advanced Packaging and Semiconductor Manufacturing, Yole Développement.

Despite the integration methods used for CMOS Image Sensors changing over the years, TSV continued to be incorporated in the packaging of these devices, increasing functionality and enabling more efficient use of its silicon space. For example, Sony used a full-filled TSV and via last approach to stack the CIS onto a CMOS die. This enabled the company to more efficiently utilise (90%) of its die surface area for the pixel array while decreasing the size of the die. This technology is using a 3D stacked integration approach, and, currently is the new trend for this type of devices as it enables a smaller die size and faster on-chip processing.

According to Yole, the path is now open for the heterogeneous integration of devices: MEMS are being integrated onto ASIC dies connected with TSVs (such as mCube, Bosch, with their accelerometer products, and others), and 3D stacked devices with integrated passives for medical applications.