MIPS made freely available for CPU architecture education

Imagination Technologies has announced a revolutionary offering as part of its Imagination University Programme (IUP), called MIPSfpga. Through MIPSfpga, Imagination is transforming CPU architecture education in universities around the globe by offering them free and open access to a fully-validated, current generation MIPS CPU in a complete teaching package.

CPU architecture is generally taught as part of electronic engineering, computer science and computer engineering courses, and is based on MIPS or one of the other two major CPU architectures. Until now, what’s been missing from all of these courses is access to real, un-obfuscated RTL code that will enable professors and students to study and explore a real CPU. Imagination is changing that with MIPSfpga, bringing a CPU architecture education paradigm to universities around the world.

The MIPS architecture was originally developed at Stanford University in the early 1980s. It has been the teaching architecture of choice for decades because of its elegant true RISC design, epitomised by Dr. David A. Patterson and Dr. John L. Hennessy in their book, ‘Computer Organisation and Design’, now in its fifth edition.

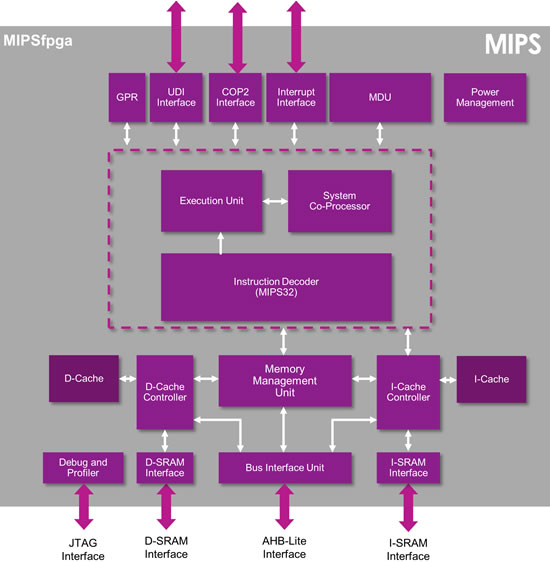

Through MIPSfpga, Imagination is providing universities with a simplified version of its popular MIPS microAptiv CPU core which has been configured by an academic specifically for academic use. Many academics are already familiar with the microAptiv CPU, and it already has a broad ecosystem of support based on its use in numerous commercial products including the PIC32MZ MCU from Microchip Technology.

The MIPS CPU is being offered as part of a complete free-to-download package for universities, together with a Getting Started Guide, teaching guide for professors, and examples designed to enable students to see how the CPU works and explore its capabilities. With the materials, students can develop a CPU and take it through debug, running on an FPGA platform.

“Currently we are teaching computer architecture in our MS course using the famous Patterson & Hennessy book,” commented Prof. K. Subbarangaiah, Director, VLSI Engineering & Design Automation IIT. “The availability of a MIPS CPU would be a fantastic practical complement to the theory we teach, and give students first-hand experience directly relevant to their future designs.”

The MIPSfpga deliverables were developed by Dr. David Harris and Dr. Sarah Harris, professors who co-wrote the popular book, ‘Digital Design and Computer Architecture’, now in its second edition. Dr. David Harris configured the MIPS CPU at the heart of MIPSfpga, and Dr. Sarah Harris developed the teaching materials.

This MIPS CPU configuration is designed to run on a low-cost FPGA platform, with guides available for theDigilent Nexys4 platform with a Xilinx Artix-7 FPGA, and the Terasic DE2 platform with an Altera Cyclone FPGA.

MIPSfpga is already running in several academic institutions including Harvey Mudd College, Imperial College London, University College London, and the University of Nevada, Las Vegas.

The MIPSfpga CPU and related materials are available for download from the Imagination University Programme website now for first phase users via an application process. To register for the IUP and learn more, click here. Phase two, starting in June, will require only a simple click-through agreement. Additional teaching materials are being developed and will be made available later this year.

Imagination is working with Xilinx through its University Programme to roll out MIPSfpga to universities worldwide. The companies are co-sponsoring workshops to enable professors to get started, with the first workshops being held at Harvey Mudd College on 13th to 14th May, 2015.

“What we’re doing through MIPSfpga is something that hasn’t been done before with a major CPU architecture,” said Tony King-Smith, Executive Vice President of Marketing, ImgTec. “We’ve been working on this programme for about a year as part of our focus revitalizing MIPS under Imagination. During that time, we have found great support for the programme, and great love for MIPS – it is the preferred architecture for teaching. MIPS started off inside of a leading university, kicking off the RISC revolution, and now we’re delighted to bring MIPS back home to the academic community, many of whom have already been using MIPS for many years.”

“It’s been more than 30 years since we created the MIPS architecture at Stanford University,” added Dr John L. Hennessy, Office of the President, Stanford University. “I am pleased to see MIPS rejuvenated under Imagination’s care, and to see Imagination rolling out this exciting programme that brings MIPS back to academia in a big way. With its pure RISC architecture based on efficiency and simple extensible design principles, MIPS is an ideal architecture for teaching and studying CPU design. Professors and students alike can benefit from the ability to study MIPS RTL code and explore a real MIPS CPU.”