Embedded and scalable CPU named 'Product of the Future'

The 'Polish Product of the Future' (Polski Produkt Przyszłosci - PPP) competition has been organised annually since 1997. Since 2008, the competition and promotion of winners has been co-financed by the European Union.

The competition’s objective is to promote and disseminate information on achievements of innovative techniques and technologies which have the opportunity to be applied in the global market.

The competition is intended for enterprises, research and development units, scientific institutes, research centres and also for individual inventors from EU Member States.

The Award Gala was held on 30th November in Warsaw, Poland, where DCD’s CEO, Jacek Hanke received the award from the hands of Patrycja Klarecka, PAED’s CEO. "We’ve designed the D32PRO from scratch, basing on our best experience both from our World’s Fastest 8051 and several other innovative IP Cores," said Jacek Hanke, CEO, Digital Core Design. "The D32PRO is silicon proven, fully scalable and like all other DCD’s IP Cores – royalty-free."

DCD’s 32-bit CPU has been awarded by Polish Agency for Enterprise Development not only for the performance, small footprint (starting at 10.6k/6.8k ASIC gates) and high clock frequency (up to 1GHz in modern ASIC technologies) but most of all for flexible licensing methods. "Starting from 1999, all of our IP Cores are royalty-free," said Jacek Hanke, "many of our customers emphasised the lack of royalty-free 32-bit IP Cores, so… we made a step further and offer D32PRO in a royalty-free model and flexible Fast Track License."

All peripherals on board

The D32PRO has been equipped with a Floating Point Coprocessor and a variety of available peripherals, e.g. USB, Ethernet, I2C, SPI, UART, CAN, LIN, RTC, HDLC, Smart Card. It is easy to add other peripherals to the CPU.

3-stage pipeline – ultimate code density

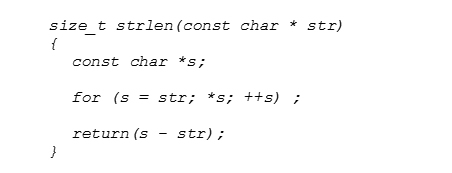

The D32PRO is a universal and fully configurable solution, which effectively executes application codes with both many jumps (e.g. switch tree) and homogeneous (e.g. arithmetic operations). This wouldn’t be possible without variable pipelining. Another innovation lies in the command list, which is based on special instructions – derivatives to the higher level language, e.g. C. This enables ultimate code density, which goes in hand with a short and compact command list. The FZB instruction seems to be the best example:

In most 32-bit CPUs it would be possible to find an optimisation which enabled one to check four bites in register at the same time:

![]()

But the real power comes with the FZB instruction implemented in the D32PRO. Now you can search the register with one one-cycled instruction:

![]()

The D32PRO has been equipped with 13 general registers R0-R12 and most of them are refreshed automatically after interruption. Thanks to this, the CPU accelerates interrupts and context switching in the real time systems. And if that's still not enough, the D32PRO has been equipped with one non-maskable and several real-time reconfigurable interrupts: like its activity, priority level and number of automatically stacked registers.

Low power for (not only) IoT

Modern 32-bit CPUs should be designed with a special concern for power-performance ratio. That’s why the D32PRO emphasises low power consumption. This wouldn’t be possible without a special PMU (Power Management Unit), which controls the clock’s frequency. Thanks to it an engineer can programme a power-saving mode for the CPU, where all the peripherals will be working with nominal clock. Moreover, the CPU itself can be moved to the STOP mode, with the clock detached from it. Then it can return to the normal mode by an interrupt from any peripheral. It is not a problem for the CPU to switch off the peripherals which are unused at the moment and save additional power.

Debugger – bootloader

The D32PRO, similarly to DCD’s 8051 IP Cores, is delivered with a built-in hardware debugger. But this special solution has been tailored for 32-bit CPU, that’s why it enables full control from Eclipse level (complete Eclipse debugging system, GCC => USB 2.0 cable => D32PRO). Moreover, in DCD’s debugger only two pins have been used, when in competitive solutions communication requires the use of at least five pins (JTAG). The hardware bootloader unit enables firmware program memory saving directly from external Flash memory connected through an SPI interface. Moreover, the bootloader has been equipped with a hardware encryption tool stored in non-volatile memory. It can protect firmware against reverse engineering.